# (a) al

#### INDEX

Introduction

Specification W7993-725 Terminal

Specification W7993-800 CPU W7993-864 64K RAM

Specification W7993-320  $5\frac{1}{4}$ " Floppy Disk Drives

Specification W7993-401 Power Supply

Appendix

#### INTRODUCTION

WYNCHESTER SYSTEMS AND ELECTRONICS INC. is the designer and manufacturer of the W7993 series of small computer systems. Using stable design concepts the products offer a low cost vehicle for systems houses that develop custom programs for either straight line applications or specific end users. The W7993 uses industry standards both in the architecture and the operating system and therefor is compatible with the majority of similar systems on the market. Compatibility is important in both hardware and software in the fast moving micro computer environment, allowing full advantage to be taken of new devices and methods that are continually being offered both by the semiconductor manufacturers and the many software houses.

In the competitive environment of small computers, the W7993 represents the best price performance of any system on the market today.

SPECIFICATION

W7993-725 - TERMINAL

#### W7993-725 TERMINAL

#### Installation

The 725 should be positioned on a steady surface at a comfortable level for the user. A space of at least three inches should be provided at the rear of the 725 to provide ease of access to the power switch and brightness control. Care should be taken to keep the ventillation holes on the top rear and underside from becoming blocked. The line cord should be plugged into a three pin grounded outlet.

The 725 power switch (located on the rear) should illuminate when turned on. After a one minute warm-up period the monitor should display a block cursor in the upper left corner of the screen. This position will be referred to as the HOME or HOME-UP position throughout this manual. If the cursor does not appear in the home position of an otherwise clear screen, depress the [CLEAR] Key. If the cursor still does not appear, refer to Section 8 of this manual.

Depress the [LINE/LOCAL] key on the keyboard. Type on the keyboard. Characters will appear corresponding to the keys you strike and the cursor will advance to indicate the next position into which a character will be written.

Adjust the brightness control on the rear of the 725 cabinet for suitable viewing while maintaining a black background. Excessive brightness can cause premature phosphor degradation or "burning" not covered under the CRT warranty. When leaving displayed data on the screen for extended periods of time (overnite for example), reducing the brightness will prolong the CRT lifetime.

## 1.1 Using the 725 Operation Manual

All the information necessary to realize the full potential of this product is contained in this operating manual. We strongly urge you to read the manual thoroughly before you use the terminal.

- Section 2: describes the various emulations available.

- Section 3: details the operation of the keyboard and describes the operation of all function keys as well as the numeric cluster.

- Section 4: lists the features offered by the 725 and describes each feature in alphabetical order. Should you encounter problems when attempting to use a particular feature of the 725 you may refer to its description in Section 4 for clarification.

- Section 5: describes the Input/Output and Auxilliary interfaces. Information contained in this section is useful to insure compatibility between the 725 and your host computer.

- Section 6: explains the user selectable options which include: terminal emulation, ADM 3A wrap or no wrap, and video attribute selection. Instructions are provided for changing these options to meet your specific tastes or application.

- Section 7: contains the Appendices which include the following useful information, a complete list of available features in each of the three terminal emulation modes; tables for use with the cursor positioning features; a complete list of the ASCII codes including their Hexidecimal, Octal, Binary and Decimal equivalents.

#### 2.0 Operating Modes

For efficient communications, the Local mode with associated editing features may be utilized to minimize use of costly host CPU time or to minimize the number of packets transmitted in a pay-by-the-packet system. The Local mode can also be used for testing and studying the operation of various terminal features.

#### 2.1 Terminal Emulation Selection

The 725 may be commanded to emulate one of three terminals: The Lear Seigler ADM 3A, Hazeltine 1400, or 725. Mode switches 1 and 2 (1.0.1 and 1.0.2) select the terminal to be emulated as follows:

| <u>T.O.1</u> | <u>T.0.2</u> | <u>Emulation</u> |

|--------------|--------------|------------------|

| OFF          | OFF          | 725 WRAP*        |

| OFF          | ON           | 1410 WRAP*       |

| ON           | OFF          | ADM 3A NO WRAP   |

| ON           | ON           | ADM 3A WRAP*     |

Wrap/No Wrap refers to the action taken when the last position on the line is filled with a displayable character. To wrap is to proceed filling the next line; to not wrap is to leave the cursor in the last column and "overprint" characters.

#### 2.2 Local Self Test

The LOCAL mode also provides a means of testing the terminal manually. If the terminal works in the LOCAL mode, any problems are limited to either the 725 interface, the communication link between the 725 and the host computer, or the host computer.

#### 2.3 Transparency Mode

A very useful feature of the 725 is its capability to display a unique symbol for each of the ASCII control codes when in the Display Control Code mode. This mode can be entered and exited only by depressing the [CTRL] and [Q] keys simultaneously while in the LOCAL mode. This aids both the receive and transmit operations. On the receive side it permits one to identify every character received by the terminal settling any format problems caused by otherwise unseen control characters. On the transmit side it allows control characters to be imbedded in the displayed data for transmission in block mode to the computer or printer.

#### 3.0 Keyboard

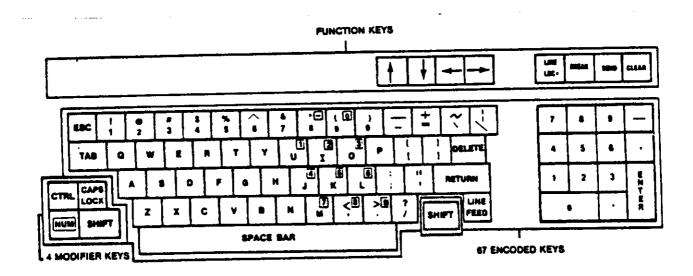

The 725 keyboard contains 80 keys which may be classified as either encoded, modifier, or function keys (see Figure 3.1 below).

The keyboard features typamatic (Auto-Repeat) operation at a rate of 30 characters per second (CPS) after a one second delay.

#### 3.1 Encoded and Modifier Keys

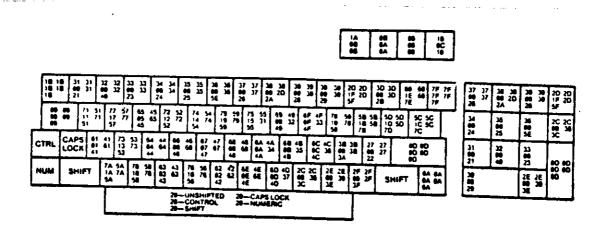

The majority of keys on the keyboard generate an output code when struck. The assignment of output codes to keys is illustrated in Figures 3.1 and 3.2. Note that the output codes generated by the encoded keys depend on the state of the four modifier keys-[CAPS/LOCK], [CTRL], [NUM], and [SHIFT]. The modifier keys do not generate output codes when they are depressed.

NOTE: The encoded key [ESC] and the modifier key [CTRL] have special significance to 725 and appear frequently in this manual in conjunction with another key e.g. [ESC] [H], [CRTL] [G]. The

[ESC] key (because it is an encoded key), should be depressed and released before striking the [H] key in the above example but the [CTRL] key (because it is a modifier key) must be depressed and held down while simultaneously striking the [G] key and released after the [G] key is released.

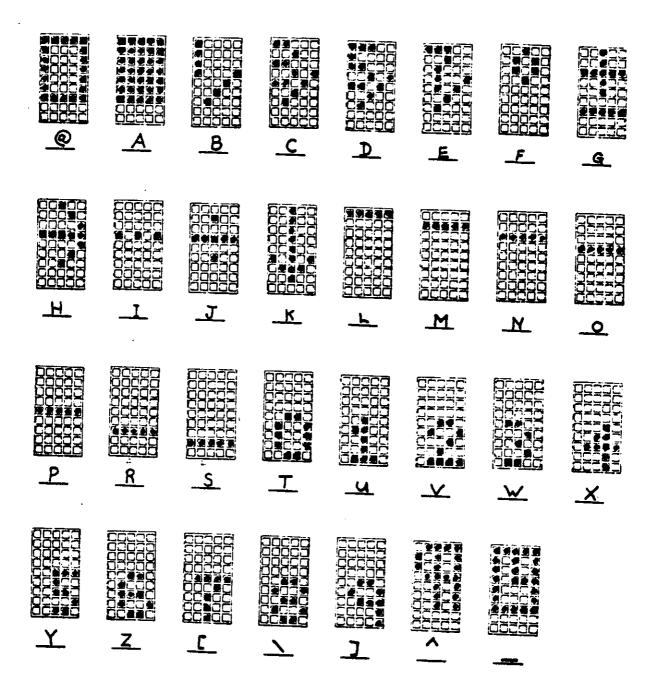

Figure 3.2 Keyboard Output Codes

Section 3

#### 3.2 Function Keys

The top row of eight keys on the 725 keyboard may generate output codes but are primarily used to control various functions. These functions are described below.

#### 3.2.1 [Line/Loc.] Key

This key controls whether the 725 is in the ON-LINE OR LOCAL mode. When ON-LINE (key up), all codes generated by the encoded key are transmitted out the I/O and AUX ports is accepted and displayed. When in the LOCAL mode (key down), all codes generated by the encoded keys are "echoed" to the screen and are not transmitted out either the I/O or AUX ports. Data may be sent out these ports when in the LOCAL mode by invoking a SEND command as described in Section 3.2.5 below.

#### 2.2.2 Cursor Control Keys

In LOCAL mode, these keys move the cursor in the indicated direction without transmitting any codes to the host. These keys peg the cursor at the screen boundaries.

In the ON LINE mode, each cursor control key transmits a unique sequence of codes dependent upon the emulation status of the terminal. The following table lists the cursor control key output codes for the various emulation modes.

| <u>Key</u>    | <u>725</u>       | ADM 3A                     | <u>H1410</u>               |

|---------------|------------------|----------------------------|----------------------------|

| UP<br>DOWN    | CTRL Z<br>CTRL K | CTRL K<br>CTRL J<br>CTRL H | CTRL K<br>CTRL J<br>CTRL H |

| LEFT<br>RIGHT | CTRL H<br>CTRL X | CTRL L                     | CTRL P                     |

NOTE: There are two differences between the Hazeltine 1410 cursor movement and the 725 emulation: the cursor up function has been added to the 725; when moving left and right the cursor does not wrap to the previous or next lines as on the 1410.

#### 3.2.3 Break Key

This key forces the serial output to assume the space (logical O) state for as long as it is depressed.

#### 3.2.4 Clear Key

Depressing the clear key causes the 725 to clear the screen and to read the setting of the MODE SELECT switches described in Section 2.1 above.

#### 3.2.5 <u>Send Key</u>

This key commands the 725 to transmit the contents of its screen out pin 2 of its  $\rm I/O$  and AUX communication ports.

NOTE: While sending the 725 ignores characters received from the host computer. When in the LOCAL mode if no data is being sent to the computer in the block transmission mode the 725 will accept and process data from the host. This allows the user to edit the data on the screen, send it and receive a response from the host without changing the position of the [LINE/LOC.] keyswitch. It also insures that any messages from the computer are not lost while in the LOCAL mode.

#### 3.2.6 Delete Key

When this key is pressed in the local mode, the character immediately to the left of the cursor is erased from the screen. When struck in the on-line mode, the code [7f] is transmitted.

#### 3.3 Numeric Data Entry

There are three methods provided by the 725 keyboard for facilitating the entry of numeric data. These are: typewriter style - the numbers 1 through 9 and 0 appear in the top row of the main keyboard just as on a modern typewriter; calculator style - a 14 key calculator format numeric pad is provided for accounting type data entry; keypunch style - when the [NUM] key is depressed, a numeric key cluster identical to the IBM Model 29 keypunch format is available inlaid in the main keypad. This feature is especially attractive to keypunch operators since they need not sacrifice their speed learning the calculator format. To disable the [NUM] key, it should be pressed again and it will disengage.

NOTE: When the [NUM] key is down and the [8] key is depressed in the 14 key numeric pad, the code for a - will be generated. Similarly, if the [9] key is struck in the 14 numeric pad and the [NUM] key is down, the code for a 0 will be generated. This is due to the fact that the 14 keys in the numeric pad are functionally indistinguishable from 14 keys in the main keypad. The pairing of numeric pad keys and main pad keys is:

| Numeric<br>Pad Key                                          | Same as | Main<br>Pad Key                                                                                                         |

|-------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------|

| [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [.] [.] [-] [ENTER] |         | [)/0]<br>[!/1]<br>[@/2]<br>[#/3]<br>[\$/4]<br>[%/5]<br>[&/7]<br>[*/8-]<br>[(/90]<br>[/.9]<br>[/.8]<br>[-/-]<br>[RETURN] |

#### 4.0 Response To Control Codes and Escape Sequences

Numbers shown in braces (e.g (07)) represent the Hexadecimal equivalent of the associated ASCII code.

The symbol N/A is used to indicate that the feature is not available in the selected emulation mode.

The Lead-In character for the Hazeltine 1410 mode may be either an ESCAPE (7F) or TILDE (7E). Throughout this section, the ESCAPE is assumed as the Lead-In character.

#### 4.1 Absolute Cursor Positioning (Direct Cursor Addressing)

ABSOLUTE CURSOR POSITIONING allows the user to position the cursor anywhere within the 24 x 80 display matrix. The general format is a lead-in code, or codes, followed by two address co-ordinates. These co-ordinates must be transmitted to the terminal in ASCII. The cursor assumes the new position after the co-ordinates have been given. No other coding may be imbedded within this string of characters.

NOTE: Please refer to Appendix 7.2 for the ABSOLUTE CURSOR ADDRESSING TABLES and Appendix 7.3 for a complete list of decimal/hex/ASCII conversions.

#### 4.1.1 725 Cursor Positioning

To position the cursor, the ASCII code (14) must be received followed by the appropriate line # (0-23) and the column # (0-79). If an invalid line is received, it is reduced modulo 24 until a valid line 0-23 is produced. Similarly, an invalid column is reduced modulo 80. The top line of the display is line, 0; the leftmost column is column 0.

EXAMPLE: To position the cursor, on the tenth line down and in the fifth column from the left, the following codes must be received by the terminal.

| <u>Keys</u> | [CTRL] [T] | [CTRL] [I/2] | [CTRL] [D] |

|-------------|------------|--------------|------------|

| Codes       | (14)       | (09)         | (04)       |

#### 4.1.2. ADM 3A Cursor Positioning

To position the cursor, the ASCII codes (1B) (ESC) and (3D) (=) must be received followed by the appropriate row number ASCII codes (40) through (77) and column number (codes (20) through (6F)).

EXAMPLE: To position the cursor on the tenth row down and in the fifth column from the left, the following codes must be received by the terminal.

| Keys  | [ESC] [+/=] | [1/2] | [\$/4] |

|-------|-------------|-------|--------|

| Codes | (1B) (3D)   | (49)  | (24)   |

#### 4.1.3 Hazeltine 1410 Cursor Positioning

To position the cursor, the ASCII codes (1B) (11) must be received followed by the appropriate column number and row number. The 80 columns range from 0 to 79, and the rows range from 0 to 23.

The column addresses are modulo (60) as follows:

| Hexadecimal Address                   | <u>Column (Decimal)</u> |  |

|---------------------------------------|-------------------------|--|

| (0) through (4E)<br>(4F) through (5F) | 0 through 78<br>79      |  |

| (60) through (7F)                     | 0 through 31            |  |

The row addresses are molulo (20) as follows:

| Hexadecimal Address | Row (Decimal) |

|---------------------|---------------|

| (0) through (16)    | 0 through 22  |

| (17) through (1F)   | 23            |

| (20) through (36)   | 0 through 22  |

| (37) through (38)   | 23            |

| (40) through (56)   | O through 22  |

| (57) through (5F)   | 23            |

| (60) through (76)   | 0 through 22  |

| (77) through (7F)   | 23            |

#### 4.2 Backspace

This will cause the cursor to move one character position to the left without erasing data on the screen. When the cursor reaches to leftmost column it will stop.

|         | <u>725</u>         | ADM3A                 | <u>H1410</u>          |

|---------|--------------------|-----------------------|-----------------------|

| Key(s)  | [CTRL] [H] or [<-] | [CTRL] [H]<br>or [<-] | [CTRL] [H]<br>or [<-] |

| Code(s) | (08)               | (08)                  | (80)                  |

#### 4.3 Bell

When the BELL code is received, an audible tone of 1760 hertz is generated for one half second. The cursor position is not affected.

|         | <u>725</u> | ADM 3A     | <u>H1410</u> |

|---------|------------|------------|--------------|

| Key(s)  | [CTRL] [G] | [CTRL] [G] | [CTRL] [G]   |

| Code(s) | (07)       | (07)       | (07)         |

#### 4.4 Carriage Return

LOCAL: The cursor is moved to the leftmost position of the next line. If it is on the bottom line, the screen will scroll.

LINE: The cursor is moved to the leftmost position on the present line except in the H1410 mode. In the H1410 mode, a RETURN code causes a carriage return and line feed operation.

|         | <u>725</u>                  | ADM 3A                      | H1410                    |

|---------|-----------------------------|-----------------------------|--------------------------|

| Key(s)  | [RETURN]<br>or [CTRL] [M/7] | [RETURN]<br>or [CTRL] [M/7] | [RETURN] or [CTRL] [M/7] |

| Code(s) | (OD)                        | (OD)                        | (OD)                     |

#### 4.5 Cursor Down

On receipt of the CURSOR DOWN command, the cursor is moved down one line in the same column. If the cursor is on the bottom line of the screen, the position of the cursor will not change nor will the display scroll.

|         | <u>725</u>   | ADM 3A | H1410 |

|---------|--------------|--------|-------|

| Key(s)  | [CTRL] [K/5] | N/A    | N/A   |

| Code(s) | (OB)         |        |       |

#### 4.6 Cursor Right

The cursor advances one column to the right. The display is not altered. If in the last column it will not move.

|         | <u>725</u>            | ADM 3A                 | H1410                |

|---------|-----------------------|------------------------|----------------------|

| Key(s)  | [CTRL] [X]<br>or [- ] | [CTRL] [L/6]<br>or [-] | [CTRL] [P]<br>or [-] |

| Code(s) | (18)                  | (00)                   | (10)                 |

#### 4.7 Cursor Up

On receipt of the CURSOR UP command, the cursor is moved up one line in the same column. If the cursor is on the top line of the screen, the position of the cursor will not change.

|         | 725                        | ADM 3A                       | <u>H1410</u>                 |

|---------|----------------------------|------------------------------|------------------------------|

| Key(s)  | [CTRL] [Z]<br>or Cursor Up | [CTRL] [K/5]<br>or Cursor Up | [CTRL] [K/5]<br>or Cursor Up |

| Code(s) | (1A)                       | (08)                         | (OB)                         |

#### 4.8 Delete Character

Delete the character denoted by the cursor. All characters to the right of the cursor position are moved left by one column. The rightmost position is cleared to the video attribute of the last character on the line. Since the DELETE functions take several milliseconds to execute, it is recommended that they be used in the LOCAL mode from the keyboard. When sending the DELETE CHARACTER or DELETE LINE codes from the computer, filler codes must be used.

|         | 725        | ADM_3A | H1410 |

|---------|------------|--------|-------|

| Key(s)  | [CTRL] [D] | N/A    | N/A   |

| Code(s) | (04)       |        |       |

#### 4.9 Delete Line

All data on the line denoted by the cursor is eliminated. Pre-existing data below the cursor is moved up one line and the bottom line is cleared to the present attribute type. When deleting lines the cursor must not be positioned in the first column. See note in DELETE CHARACTER.

|         | <u>725</u> | ADM 3A | <u>H1410</u> |

|---------|------------|--------|--------------|

| Key(s)  | [CTRL] [W] | N/A    | N/A          |

| Code(s) | (17)       |        |              |

#### 4.10 Erase To End of Frame (EEOF)

All characters from the cursor position to the end of the screen are erased to spaces of the present video attribute type. The cursor position is not affected.

|         | <u>725</u>                  | ADM 3A | <u>H1410</u> |

|---------|-----------------------------|--------|--------------|

| Key(s)  | [CTRL]<br>[SHIFT]<br>[-/-1] | N/A    | N/A          |

| Code(s) | (1F)                        |        |              |

#### 4.11 Erase To End of Line (EEOL)

All positions from the cursor to the right margin are replaced by spaces of the present video attribute type.

|         | <u>725</u>                 | ADM 3A | H1410 |

|---------|----------------------------|--------|-------|

| Key(s)  | [CTRL]<br>[SHIFT]<br>[6/^] | N/A    | N/A   |

| Code(s) | (1E)                       |        |       |

#### 4.12 Home

This function moves the cursor to the upper left corner of the screen.

|         | <u>725</u>   | ADM 3A                  | H1410            |

|---------|--------------|-------------------------|------------------|

| Key(s)  | [CTRL] [)/]] | [CRTL] [SHIFT]<br>[6/^] | [ESC] [CTRL] [R] |

| Code(s) | (1D)         | (1E)                    | (1B) (12)        |

#### 4.13 Home and Clear

The screen is cleared to spaces, and the cursor is moved to the upper left hand corner of the screen.

|         | <u>725</u>   | ADM 3A     | <u>H1410</u>       |

|---------|--------------|------------|--------------------|

| Key(s)  | [CTRL] [L/6] | [CTRL] [Z] | [ESC] [CTRL] [!/\] |

| Code(s) | (OC)         | (1A)       | (1B) (1C)          |

#### 4.14 Insert Character(s)

Insert subsequent characters into the cursor row at the cursor position. After this command, all characters at the cursor position and to its right are moved one position to the right each time a displayable character is typed at the keyboard. To exit from this displayable mode, any control character may be typed. The 725 will act upon the control character and sound the BELL to indicate an exit from the insertion mode.

NOTE: Since INSERT functions take several milliseconds to execute it is recommended that they be used in the LOCAL mode from the keyboard. When sending the INSERT CHARACTER or INSERT LINE codes from the computer, filler codes must be used.

|         | . <u>725</u> | ADM 3A | <u>H1410</u> |

|---------|--------------|--------|--------------|

| Key(s)  | [CTRL] [S]   | N/A    | N/A          |

| Code(s) | (13)         |        |              |

#### 4.15 Insert Line(s)

This will allow a new line of text to be added between any two preexisting lines on the screen. A blank line will be inserted on the row denoted by the cursor. All pre-existing text on the cursor row and below is moved down by one line and the last line scrolls downward off the screen. The blank line will be cleared to spaces with the present video attribute. See note in INSERT CHARACTER.

|         | <u>725</u> | ADM 3A | H1410 |

|---------|------------|--------|-------|

| Key(s)  | [CTRL] [A] | N/A    | N/A   |

| Code(s) | (01)       |        |       |

#### 4.16 Line Feed

The cursor moves down one line in the same column. If it is on the bottom line of the screen the screen will scroll upwards.

|         | <u>725</u>   | ADM 3A       | H1410        |

|---------|--------------|--------------|--------------|

| Key(s)  | [CTRL] [J/4] | [CTRL] [J/4] | [CTRL] [J/4] |

| Code(s) | (DA)         | (OA)         | (OA)         |

#### 4.17 Lock Keyboard

After receipt of this command the keyboard will not generate any output codes until either an unlock command is received or the [CLEAR] key is struck.

|         | <u>725</u> | ADM 3A       | <u>H1410</u>     |

|---------|------------|--------------|------------------|

| Key(s)  | N/A        | [CTRL] [0/3] | [ESC] [CTRL] [U] |

| Code(s) |            | (OF)         | (1B) (15)        |

#### 4.18 New Line

This command forces the terminal to perform a CARRIAGE RETURN and a LINE FEED.

|         | <u>725</u> | ADM 3A | H1410          |

|---------|------------|--------|----------------|

| Key(s)  | N/A        | N/A    | [CTRL] [SHIFT] |

| Code(s) |            |        | (1F)           |

#### 4.19 Null

Sending the ASCII NULL (00) is accomplished by holding the [CTRL] key down and then typing the @ sign, (') or space bar. This is generally used as a filler code and is not acted upon when received.

|        | 725    | ADM 3A         | H1410 |

|--------|--------|----------------|-------|

| Key(s) | [CTRL] | ANY NUMBER KEY |       |

# 4.20 Report Character at Cursor Position

The ASCII code for the character at the cursor position is transmitted to the computer followed by a carriage return code.

|         | 725        | ADM 3A | <u>H</u> 1410    |

|---------|------------|--------|------------------|

| Key(s)  | [CTRL] [R] | N/A    | [ESC] [CTRL] [T] |

| Code(s) | (12)       |        | (1B) (14)        |

#### 4.21 Report Cursor Position

After receiving the appropriate command sequence, the terminal will respond by reporting the cursor's current address co-ordinates. Please refer to Appendix 7.2 for the ABSOLUTE CURSOR ADDRESSING TABLES and Appendix 7.3 for a complete list of decimal/hex/ASCII conversions.

|         | <u>725</u> | ADM 3A | <u>H1410</u>     |

|---------|------------|--------|------------------|

| Key(s)  | [CTRL] [E] | N/A    | [ESC] [CTRL] [E] |

| Code(s) | . (05)     |        | (1B) (05)        |

#### 4.22 Send Page - Remote

Sends data from the home position to the present cursor position. At the end of each line a carriage return and line feed code is sent. The SEND operation can be initiated locally by depressing the SEND key as described in Section 3.2.5.

|         | <u>725</u>                      | ADM 3A | H1410 |

|---------|---------------------------------|--------|-------|

| Key(s)  | <pre>[CTRL] [B] or [Send]</pre> | N/A    | N/A   |

| Code(s) | (02)                            |        |       |

#### 4.23 Tab - Column

The cursor will advance to the next fixed TAB stop on the present line. The fixed TAB stops are in column 8, 16, 24, 32, 41, 49, 57, 65, and 73. If the cursor is in columns 73 through 78, it will advance one column. In column 79, the cursor will not move.

|         | <u>725</u>   | ADM 3A | <u>H1410</u> |

|---------|--------------|--------|--------------|

| Key(s)  | [CTRL] [I/2] | N/A    | N/A          |

| Code(s) | (09)         |        |              |

## 4.24 Toggle Video Attribute

When this code is received the video attribute is changed. All subsequently received characters will be displayed at the new setting of the video attribute. The video attribute is user selectable to be either reduced/full intensity or normal (white characters on a black background)/reverse video. The selection of this option is described in Section 6.2.

|       | 725        | ADM 3A | H1410 |

|-------|------------|--------|-------|

| Keys  | [CTRL] [N] | N/A    | N/A   |

| Codes | (OE)       |        |       |

### 4.25 Unlock Keyboard

Receipt of this command enables the keyboard to generate output codes.

|       | <u>725</u> | ADM 3A     | H1410            |

|-------|------------|------------|------------------|

| Keys  | N/A        | [CTRL] [N] | [ESC] [CTRL] [F] |

| Codes |            | (OE)       | (1B) (06)        |

Section 5

#### 5.0 Interface Instructions

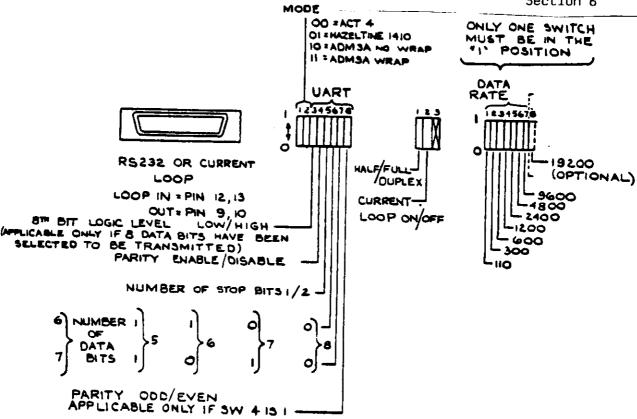

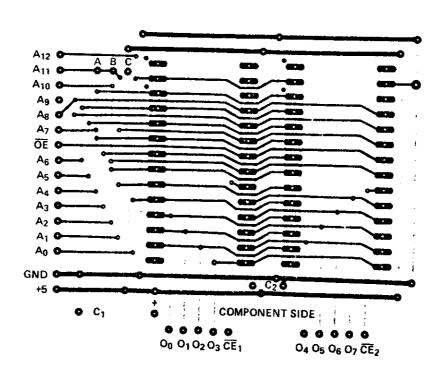

All connections and switches mentioned in the following sections are shown in Figure 5.2.

## 5.1 EIA Connector Pin Assignments

The pin assignments for the two 25 pin EIA connectors on the rear of the 725 are as follows:

#### I/O Connector:

| Pin Number                                                 | Signal                                                                                                                                                                                                                                                            |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>6<br>7<br>10<br>11 (or 9)<br>12<br>13<br>20 | Ground Serial RS232c data out of terminal Serial RS232c data into terminal Data Set Ready (into terminal) Ground Current Loop Output (+) Current Loop Output (-) Current Loop Input (+) Current Loop Input (-) Data Terminal Ready (High whenever terminal is on) |

#### AUX Connector:

| Pin Number  | Signal                                                                                     |  |  |

|-------------|--------------------------------------------------------------------------------------------|--|--|

| 1<br>2<br>3 | Ground<br>Serial RS232c data out of terminal<br>Serial RS232c data into terminal<br>Ground |  |  |

The AUXILLIARY connector provides a means of "eavesdropping" on the conversation taking place between the terminal and the computer. Pins 2 and 3 of the AUX connector are electrically connected to pins 2 and 3 of the I/O connector.

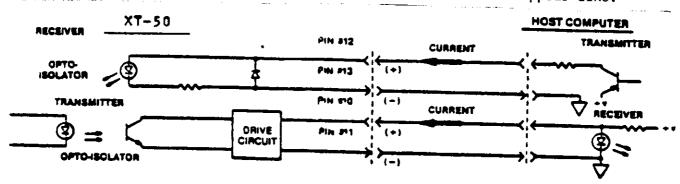

## 5.2 Current Loop Interface

An optically isolated, polarized, passive, 20mA current loop interface is available as a standard feature of the 725. In order to enable it pins 10, 11, 12 and 13 on the I/O connector must be connected to the computer as follows:

#### I/O Connector:

| Pin Number      | <u>Signal</u><br>Receiver Current input (+)<br>Receiver Current return (-) |  |

|-----------------|----------------------------------------------------------------------------|--|

| 12<br>13        |                                                                            |  |

| 10<br>11 (or 9) | Transmitter Current sink (+) Transmitter Current source (_)                |  |

In order to activate the current loop interface the switch on the rear of the terminal must be positioned properly.

Since the interface is passive, a typical installation would appear like:

Figure 5.1 Typical Current Loop Connection

# 5.3 Full and Half Duplex Operation

The 725 may operate in either full or half duplex modes. In full duplex, all characters typed at the keyboard and sent to the host computer are echoed by the host and appear on the screen. In the half duplex mode, the host does not echo the characters sent to it so the 725 provides a local echo of each transmitted character. Some modems require the half duplex mode - otherwise full duplex is usually the preferred mode of operation. A switch is provided at the rear of the terminal for selecting between the full and half duplex modes.

## 5.4 Data Rate Selection

The 725 features data transmission/reception rates of 110, 300, 600, 1200, 2400, 4800 and 9600 baud (bits/second) for the I/O and AUXILLIARY communication ports.

Figure 5.2 indicates the location of the 7 switches that select the  $\rm I/O$  dat rate. No two switches should be turned on at the same time.

| I/O    | Switch | Data Rate (Baud) |

|--------|--------|------------------|

|        |        | 9600             |

| .7     |        | 4800             |

| 6      |        | 2400             |

| 5      |        | 1200             |

| 4<br>3 |        | 600              |

| 2      |        | 300              |

| 1      |        | 110              |

| •      |        |                  |

6

#### 5.5 UART Options

8

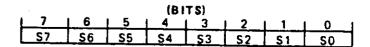

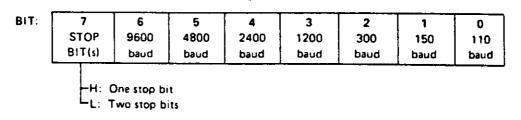

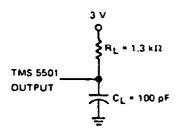

The 725 is factory set to transmit and receive a data word consisting of 1 start bit, an 8th bit (tied high on transmit, ignored on receive) and two stop bits. The parameters of the data word may be modified by resetting the UART option switches located on the logic board in the rear of the cabinet (see photo below). The UART option switches have the following effects on the data transmission format:

| UART<br>Switch # |                                         | Function                                                                                                |                                              |  |

|------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------|--|

| 3                |                                         | 8th bit transmit select: OFF (switch down) causes a logical O (space).                                  |                                              |  |

| 4                | parity; ON                              | Parity select: OFF (switch down) selects no parity; ON enables the type of parity selected by switch 8. |                                              |  |

| 5                | Number of s<br>stop bits;               | stop bits: OFF (so<br>ON selects one sto                                                                | witch down) selects 2<br>op bit.             |  |

| 6,7              | Word lengtl<br>The parity<br>word lengt | bit (if selected)                                                                                       | ,7, or 8 are possible.<br>is added on to the |  |

|                  | Length (Bits)                           | Switch 7                                                                                                | Switch 6                                     |  |

|                  |                                         | OFF<br>OFF                                                                                              | OFF<br>ON                                    |  |

Odd/Even Parity Select: OFF (switch down) selects odd parity; ON (Switch Up) selects even parity. Switch 10 must be on to enable parity generation.

ON

ON

OFF

ON

UART switches three through eight are all factory set to the off position.

#### 6.0 User Selectable Options

#### 6.1 Terminal Emulation Selection

The 725 may be commanded to emulate one of three terminals: The Lear Siegler ADM 3A, Hazeltine 1400, or 725 Mode Switches 1 and 2 (T.O.1 and T.O.2) select the terminal to be emulated as follows:

| <u>T.O.1</u>     | <u>T.0.2</u>           | <u>Emulation</u>                                           |

|------------------|------------------------|------------------------------------------------------------|

| OFF<br>OFF<br>ON | OFF<br>ON<br>OFF<br>ON | 725 Wrap*<br>1410 Wrap*<br>ADM 3A No Wrap*<br>ADM 3A Wrap* |

\*Wrap/No Wrap refers to the action taken when the last position on the line is filled with a displayable character. To wrap is to proceed filling the next line; to not wrap is to leave the cursor in the last column and "overprint" characters.

#### 6.2 Video Attribute Select

Each character in the display memory is displayed according to the video attribute that was in effect when the character was received. The video attribute may be either high or low intensity or it may be either normal or reverse video.

In order to change the video attribute from high/low intensity (the factory setting), W1 must be inserted as follows:

| W1 Connection | Video Attribute                      |

|---------------|--------------------------------------|

| S-A           | High/Low Intensity (Factory Setting) |

| S-B           | Normal/Reverse Video                 |

NOTE: Terminals with serial numbers greater than A0106061 have the video attributes switch selectable. Switch 8 in the baud rate switchpack when in the "ON" position selects High/Low Intensity; in the "OFF" position, Normal/Reverse Video is the current video attribute.

Refer to Figure 5.2.

## 7.0 Appendices

# 7.1 Function Summaries

# 7.1.1 725 Control Code Summary

| HEX Code | Control Character | Function                    |

|----------|-------------------|-----------------------------|

| 00       | <u> </u>          |                             |

| 01       | Α                 | Null                        |

| 02       | B                 | Insert Line                 |

| 04       | D                 | Send Page                   |

| 05       | E<br>E            | Delete Character            |

| 07       | G                 | Report Cursor Position      |

| 08       |                   | Bell                        |

| 09       | H                 | Backspace                   |

| OA       | I                 | Column Tab                  |

| OB       | J<br>"            | Line Feed                   |

| OC       | K                 | Cursor Down                 |

| 00       | L                 | Home and Clear to Present   |

| OD       | М                 | Attribute                   |

| OE       | • •               | Carriage Return             |

| 12       | N<br>R            | Change Attribute            |

| 13       | r<br>S            | Report Character at Cursor  |

| 14       | 5<br>T            | Insert Character            |

| 17       | · ·               | Cursor Addressing (Y,X)     |

| 18       | W W               | Delete Line                 |

| 1A       | X                 | Cursor Right                |

| 1D       | Z                 | Cursor Up                   |

| 1E       | ]                 | Home Up                     |

|          |                   | Clear From Cursor to End of |

| 1F       |                   | Line                        |

| ••       | -                 | Clear From Cursor to End of |

|          |                   | Screen                      |

# 7.1.2 ADM 3A Control Code Summary

| HEX Code                                                       | Control Character                              | Function                                                                                                                                            |

|----------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 00<br>07<br>08<br>0A<br>0B<br>0C<br>0D<br>0E<br>0F<br>1A<br>1B | @<br>G<br>H<br>J<br>K<br>L<br>M<br>N<br>O<br>Z | Function Null Bell Backspace Linefeed Cursor Up Cursor Right Return Unlock Keyboard Lock Keyboard Home and Clear Curosr Addressing (=, Column, row) |

| 1                                                              | ^                                              | Home Up                                                                                                                                             |

# 7.1.3 Hazeltine 1410 Control Code Summary

| HEX Code                               | Control Character          | Function                                                                                        |

|----------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------|

| 00<br>07<br>08<br>0A<br>0B<br>0D<br>10 | @<br>G<br>H<br>J<br>K<br>M | Nulls Bell Backspace Linefeed Cursor Up* Return (New Line)** Cursor Right Lead in Characters*** |

| 1B                                     | L                          | Lead III Characters                                                                             |

# 7.1.4 Hazeltine 1410 Escape Response Summary

| HEX Code | Control Character | Function                    |

|----------|-------------------|-----------------------------|

| 05       | E                 | Report Cursor Address       |

| 06       | F                 | Unlock Keyboard             |

| 11       | Q                 | Address Cursor, Column, Row |

| 12       | Ř                 | Home Up                     |

| 14       | T                 | Report Character at Cursor  |

| 15       | U                 | Lock Keyboard               |

| 1C       | \                 | Home and Clear Screen       |

#### Notes:

- \* The cursor up function has been added to the Hazeltine 1410 command set to allow complete cursor positioning capability.

- \*\* Per Hazeltine 1410: receipt of "return" causes a new line. Receipt of either sequence "return, linefeed" or "linefeed, return" effects a single new line (no double spacing).

- \*\*\* The lead in character may be either ESC (1B) or  $\tilde{}$  (7E).

# 7.2 Absolute Cursor Positioning Tables

# 7.2.1 725 Cursor Address Tables

| DECIMAL 0 1 2 3 4 5 6 7 8 9 10 11 12 3 4 5 6 7 8 9 10 11 12 23 24 25 27 18 29 30 31 32 33 34 40 41 42 43 44 45 50 51 52 53 | ASCH O A B C DEFENDE AND CONTRACT OF THE CONTR | ROW 0 1 2 3 4 5 5 7 8 9 10 11 2 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 12 13 14 15 16 17 18 19 20 1 2 2 3 4 5 6 7 8 9 10 1 1 12 13 14 15 16 17 18 19 20 1 12 13 14 15 16 17 18 19 10 10 10 10 10 10 10 10 10 10 10 10 10 | COLUMN  1 2 3 4 5 6 7 8 9 101 12 13 14 15 16 17 18 19 20 1 22 22 24 25 26 27 28 29 30 32 33 34 5 46 47 48 49 50 51 25 52 55 55 55 55 55 55 55 55 55 55 55 | DECIMAL 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 91 92 91 92 91 92 91 100 101 102 103 104 105 106 107 108 110 111 112 113 114 115 116 | A GABCOMFGHIJKLMNOPORSTUVWXYZL/1/1/ abodef ghilkimnopgret | ROW<br>1878901234567891011234567890112345678901123456789011234567890112345678901123456789011234567890 | COLUMN 64 65 66 67 70 77 77 77 78 79 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 21 22 23 24 26 27 28 29 30 31 23 33 34 35 35 |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 45.<br>46<br>47<br>48                                                                                                      | · 1 · 1 0 1 2 3 4 5 5 7 8 9 · · · V =/ ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21<br>22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44<br>45<br>46<br>47                                                                                                                                      | 108<br>109 -<br>110<br>111<br>112<br>113<br>114<br>115<br>116<br>117                                                                                                       | i m<br>nopqr<br>stuv<br>w                                 | 12<br>13<br>14<br>15                                                                                  | 28<br>28<br>29                                                                                                                      |

# 7.2.2 ADM 3A Cursor Address Tables

| ASCII                | CRT-POSITION     |       | ASCII<br>DECIMAL CHARACTER |            | CRT POSITION   |          |                 |

|----------------------|------------------|-------|----------------------------|------------|----------------|----------|-----------------|

| CODE                 | CHARACTER        | NOW # | COLUMN                     | CODE       |                |          |                 |

| 0                    | CTRL 0           |       |                            | 64         | •              | ٥        | 32              |

| ĭ                    | CTRL A           |       |                            | 85         | Ā              | 1        | 33              |

| 2                    | CTAL B           |       |                            | 66         |                | 2<br>3   | 34<br>35        |

| 3                    | CTRL C           |       |                            | 67<br>68   | Č              | 4        |                 |

| 4                    | CTAL D<br>CTAL E |       |                            | 69         | Ē              | 5        | 36<br>37        |

| 5<br>6               | CTAL F           |       |                            | 70         | F              | •        | 36              |

| 7                    | CTRL G           |       |                            | 71         | G              | 7        | 38<br>39<br>40  |

| •                    | CTRL H           |       |                            | 72<br>73   | H              | i        | 41              |

| 9<br>10              | CTRL I<br>CTRL J |       |                            | 74         | j              | 10       | 42              |

| 11 '                 | CTRL K           |       |                            | 75         | K              | 11       | 43              |

| 12                   | CTAL L           |       |                            | 76<br>77   | L<br>M         | 12<br>13 | 44<br>45        |

| 13                   | CTRL M           |       |                            | 76         | N              | 14       | 46              |

| 14<br>15             | CTRL N<br>CTRL O |       |                            | 79         | ö              | 15       | 47              |

| 16                   | CTAL P           |       |                            | <b>M</b> O | P              | 16       | 44              |

| 17                   | CTF Q            |       | -                          | 81<br>82   | Q<br>R         | 17<br>18 | 49<br>50        |

| 18<br>19             | CTRL R<br>CTRL S |       |                            | 83         | Ŝ              | 19       | 50<br>51        |

| 20                   | CTAL T           |       |                            | <b>4</b>   | T              | 20       | 52              |

| 21                   | CTRL U           |       |                            | 85         | U              | 21       | 53              |

| 22                   | CTRL V           |       |                            | 86<br>87   | V .<br>W       | 22<br>23 | 54<br>55        |

| 23<br>24             | CTRL W<br>CTRL X |       |                            | an an      | X              |          | 54              |

| 25                   | CTRL Y           |       |                            | 89         | Y              |          | 57              |

| 26                   | CTRL Z           |       |                            | 90         | 2              |          | 50              |

| 27                   | CTRLI            |       |                            | 91<br>92   | Į              |          | 59<br>60        |

| 28<br>29             | CTRL\<br>CTRL )  |       |                            | 93         | ì              |          | 61              |

| 30                   | CTRLA            |       |                            | 94         | $\dot{\wedge}$ |          | 62              |

| 31                   | CTRL_            |       |                            | 95         | _              |          | 63              |

| 32                   | _                |       | 0                          | 96<br>97   | `              |          | 64<br>85        |

| 33<br>34             | Į.               |       | 2 .                        | 96         | #<br>b         |          | 66              |

| 35                   |                  |       | 3                          | 99         | č              |          | 67              |

| 36                   | \$               |       | 3                          | 100        | 6              |          | 66              |

| 37                   | *                |       | 5<br>6                     | 101<br>102 | •              |          | <b>69</b><br>70 |

| 38<br>39             |                  |       | 7                          | 103        | ģ              |          | 71              |

| 40                   | (                |       |                            | 104        | h              |          | 72              |

| 41                   | j                |       | 9                          | 105        | į              |          | 73<br>74        |

| 42                   | •                |       | 10<br>11                   | 106<br>107 | j<br>K         |          | 75              |

| 43<br>44             | <b>.</b> *       |       | 12                         | 108        | ī              |          | 76              |

| 45                   | _                |       | 13                         | 109        | m              |          | 77              |

| 45                   | :                |       | 14<br>15                   | 110<br>111 | n<br>o         |          | 78<br>79        |

| 47<br>48             | 0                |       | 15<br>1 <b>6</b>           | 112        | P              |          | ••              |

| 49                   | 1                |       | 17                         | 113        | 9              |          |                 |

| 50                   | 2                |       | 18                         | 114        | 1              |          |                 |

| 51                   | 3                |       | 19<br>20                   | 115<br>116 | 1              |          |                 |

| 52<br>43             | 4                |       | 21                         | 1117       | ù              |          |                 |

| 53<br>54<br>56<br>56 | 5<br>6<br>7<br>8 |       | 22<br>23                   | 118        | Ÿ              |          |                 |

| 55                   | Ť                |       | 23                         | 119        | w              |          |                 |

| 56                   | 8                |       | 24<br>25                   | 120<br>121 | x<br>y         |          |                 |

| 57<br>58             | 9                |       | 25<br>26                   | 122        | ž              |          |                 |

| 59                   | :                |       | 27                         | 123        | Ĩ              |          |                 |

| 60                   | Ċ.               |       | 26                         | 1 124      | Ļ              |          |                 |

| 61                   | •                |       | 29<br>30                   | 125<br>126 | <u>}</u>       |          |                 |

| 62<br>63             | ;<br><<br>><br>? |       | 31 ,                       | 9          |                |          |                 |

| •                    | ,                |       | <del>-</del>               | l          |                |          |                 |

|                      |                  |       |                            | i .        |                |          |                 |

# 7.2.3 Hazeltine 1410 Cursor Address Tables

| ASCII                                                                                                                                                                            | CF                                                                                                                                                                                                                                                                                                                                | T POSI                                                                                                                             | TION                                                                                                                                                                                                     | I ASC                                                                                                                                                                                                                       | 1 <u>t</u>                            | CRT P                                                                                                                              | OSITION                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DECIMAL                                                                                                                                                                          | CHARACTER                                                                                                                                                                                                                                                                                                                         | ROW #                                                                                                                              | COLUMN #                                                                                                                                                                                                 | DECIMAL                                                                                                                                                                                                                     | CHARACTER                             | NOW #                                                                                                                              | COLUMN                                                                                                                                                                       |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>17<br>18<br>19<br>21<br>22<br>23<br>24<br>25<br>27<br>28<br>29                             | GTRL G GTRL B GTRL B GTRL C GTRL C GTRL G GTRL G GTRL G GTRL G GTRL G GTRL D GTRL C | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29                                   | CODE<br>64<br>65<br>66<br>67<br>68<br>69<br>70<br>71<br>72<br>73<br>74<br>75<br>78<br>77<br>80<br>81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>92                                                      | ØABCOERGX-JKLMZOPQRSTU>¥XYNL/I        | 0<br>1<br>2<br>3<br>4<br>5<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23           | 64<br>66<br>66<br>67<br>68<br>69<br>70<br>71<br>72<br>73<br>74<br>75<br>76<br>77<br>78                                                                                       |

| 30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50<br>51<br>52<br>53<br>54<br>55<br>56<br>61<br>62<br>63 | CTRL                                                                                                                                                                                                                                                                                                                              | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>17<br>18<br>19<br>20<br>21<br>22<br>23       | 30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50<br>51<br>52<br>53<br>54<br>55<br>56<br>57<br>58<br>59<br>60<br>61<br>62<br>63 | 93<br>94<br>95<br>95<br>96<br>97<br>98<br>99<br>100<br>101<br>102<br>103<br>104<br>105<br>106<br>107<br>108<br>110<br>111<br>112<br>113<br>114<br>115<br>118<br>117<br>118<br>119<br>120<br>121<br>122<br>123<br>124<br>125 | - < Transfer on the Ecoporatus ways ( | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30 |

The recommended cursor addresses are shown in the outlined areas they are the codes produced when the cursor address is requested. Other codes send will produce the row & column indicated.

```

Hexadecimal

Hexadecimal

Character

Decimal

~0

~0

086

58

126

01010110

053 043 2B

00101011

000 000

00

57

127

087

00000000

01010111

W

NUL

054 044

2C

00101100

001 001 01

01011000

130 088 58

00000001

055 045 2D

X

SOH

00101101

002 002 02

131 089 59

00000010

01011001

STX

00101110 056 046 2E

003 003 03

01011010 132 090 5A

00000011

Z

00101111 057 047

ETX

2F

004 004 04

133 091 5B

00000100

EOT

00110000 060 048 30

01011011

0

005 005 05

01011100

134 092

5C

00000101

ENQ

061 049 31

E

00110001

006 006 06

135 093 5D

00000110

01011101

00110010 062 050 32

ACK

007 007 07

2

136 094 5E

00000111

01011110

00110011 063 051 33

G

BEL

٨

3

010 008 08

137 095 5F

00001000

01011111

00110100 064 052 34

BS

Н

011 009 09

01100000 140 096 60

00001001

HT

00110101 065 053 35

5

00001010 012 010 0A

01100001 141 097 61

LF

00110110 066 054

36

8

6

013 011 0B

01100010 142 098 62

00001011

VT

b

00110111 067 055

37

7

00001100 014 012 0C

01100011

143 099 63

00111000 070 056 38

FF

8

015 013 0D

100 64

00001101

01100100 144

d

CR

00111001 071 057

39

9

016 014 0E

145 101 65

00001110

01100101

SO

00111010 072 058

3A

017 015 OF

01100110 146 102 66

00001111

SI

00111011 073 059 3B

1

<

020 016 10

01100111 147 103 67

00010000

Q0111100 074 060 3C

DLE

٥

021 017 11

150 104 68

00010001

01101000

DC1

Q

00111101 075 061

30

h

<u>-</u>

151 105 69

022 018 12

Ř

00010010

01101001

DC2

00111110 076 062

3E

ı

023 019 13

00010011

01101010

152 106

6A

DC3

077 063 3F

S

00111111

?

024 020 14

6B

DC4

00010100

153 107

01101011

100 064 40

01000000

0

025 021 15

154 108 6C

NAK 00010101

01101100

101 065 41

1

01000001

Ã

155 109 6D

026 022 16

00010110

01101101

SYN

01000010

m

102 066 42

B

00010111

027 023 17

01101110

156 110 6E

ETB

103 067 43

n

01000011

C

00011000 030 024 18

157 111 6F

01101111

104 068 44

CAN

0

01000100

D

00011001 031 025 19

01110000 160 112 70

EM

01000101 105 069 45

Þ

Ε

00011010 032 026

1A

161 113 71

01110001

SUB

01000110 106 070 46

q

033 027 1B

00011011

01110010

162 114

72

ESC

107 071 47

ſ

01000111

G

00011100 034 028 1C

01110011

163 115

73

110 072 48

FS

01001000

н

00011101 035 029 1D

74

GS

01110100

164 116

01001001 111 073 49

ŧ

00011110 036 030 1E

ı

165 117

75

01110101

RS

01001010 112 074 4A

u

00011111 037 031 1F

J

01110110

166 118 76

US

01001011 113 075 4B

٧

00100000 040 032 20

Κ

167 119 77

SP

01110111

01001100 114 076 4C

W

L

00100001 041 033 21

170 120 78

01111000

01001101 115 077 4D

X

M

00100010 042 034

22

171 121 79

01111001

01001110 116 078 4E

y

N

043 035 23

00100011

01111010

172

122

7A

117 079 4F

0

01001111

00100100 044 036 24

173 123 7B

01111011

01010000 120 080 50

P

25

045 037

00100101

174 124

7C

01111100

121 081 51

01010001

Q

00100110 046 038 26

175 125 7D

01111101

01010010 122 082 52

R

047 039

27

01111110 176 126 7E

00100111

123 083

53

01010011

S

00101000 050 040

28

127

01111111 177

01010100 124 084 54

T

051 041

29

00101001

01010101 125 085 55

u

00101010 052 042 2A

CTRL ABBR.

DESCRIPTION

CTRL ABBR. DESCRIPTION

CTRL ABBR. DESCRIPTION

synchronous idle

SYN

-- vertical tabulation

VT

ĸ

NUL - null, or all zeros

- end of transmission block

ETB

W

- torm feed

FF

start of heading

SOH

CAN - cancel

Х

- carriage return

CR

- start of text

M

- end of medium

STX

EM

- shift out

N

SO

- end of text

- substitute

SUB

ETX

- shift in

- end of transmission O

SI

EOT

- escape

ESC

DLE - datalink escape

P

- enquiry

- file separator

ENQ

FS

- device control 1 (X ON)

DC1

Q

- acknowledge

- group separator

ACK

1

GS

- device control 2

R

DC2

- record separator

- bell

- device control 3 (X OFF) A

RS

BEL

DC3

S

BS

backspace

US

- unit separator

- device control 4

- horizontal tabulation T DC4

HT

SP

- space

U NAK - negative acknowledge

- line feed

DEL

- delete

LF

```

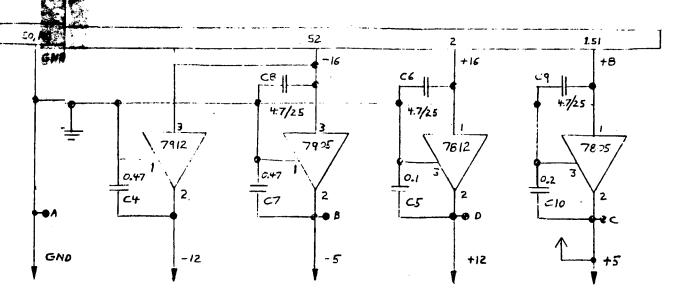

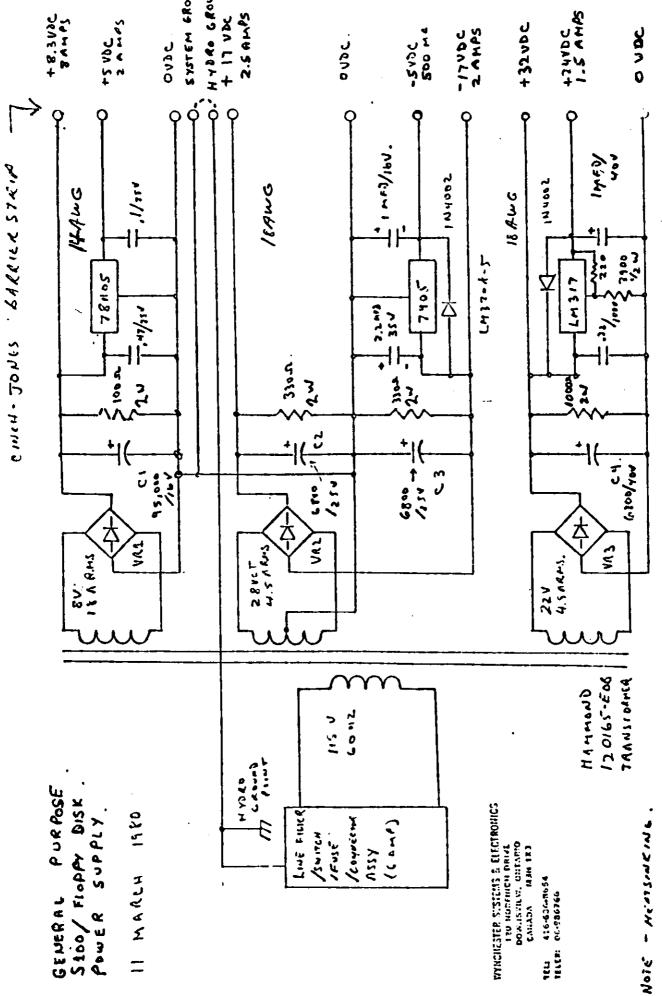

SPECIFICATION

W7993-800 - C.P.U.

W7993-864 - 64K DYNAMIC RAM

|  |  |  | *      |

|--|--|--|--------|

|  |  |  |        |

|  |  |  |        |

|  |  |  |        |

|  |  |  |        |

|  |  |  |        |

|  |  |  | 1 agus |

|  |  |  |        |

|  |  |  |        |

|  |  |  |        |

|  |  |  |        |

|  |  |  |        |

|  |  |  |        |

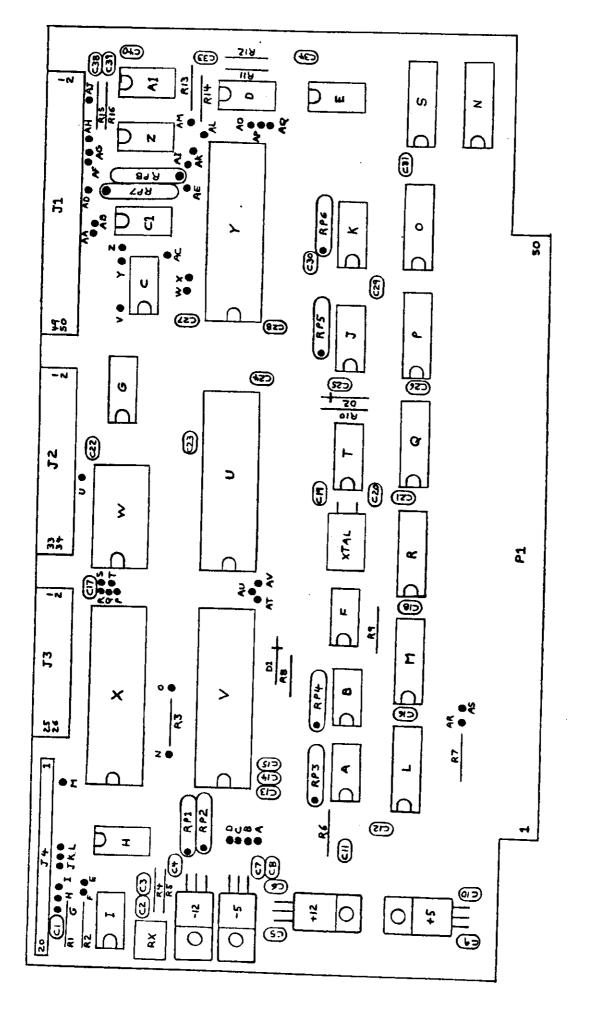

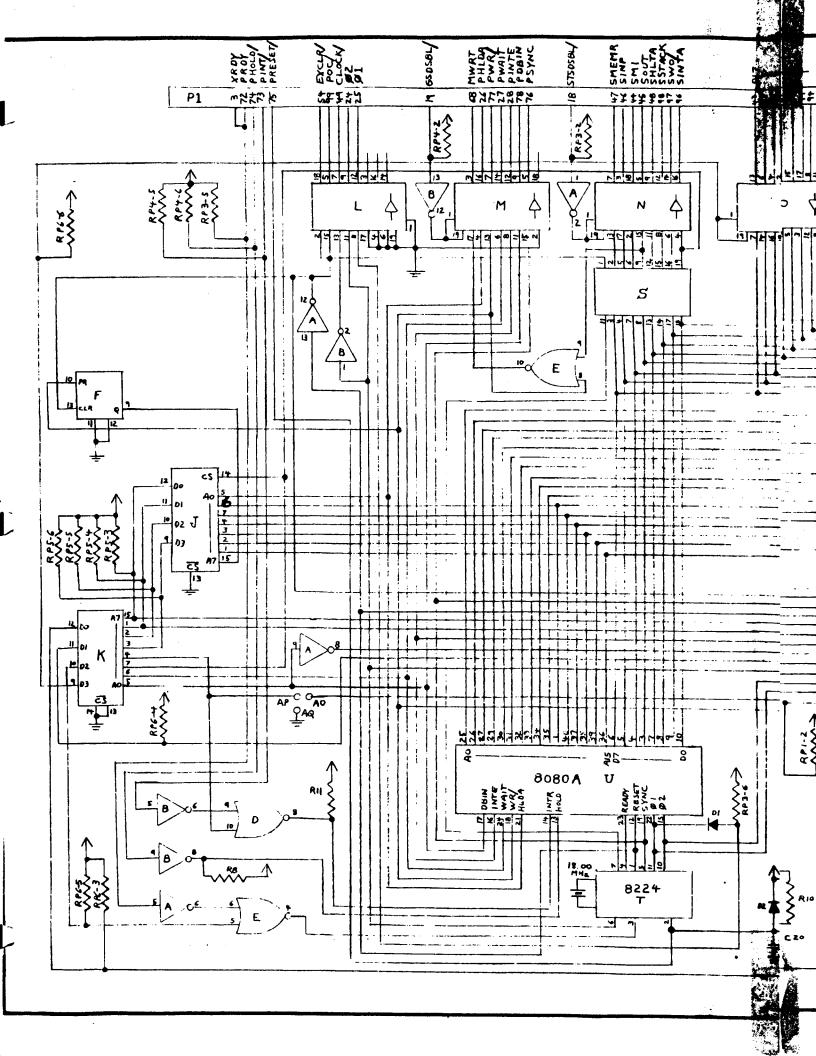

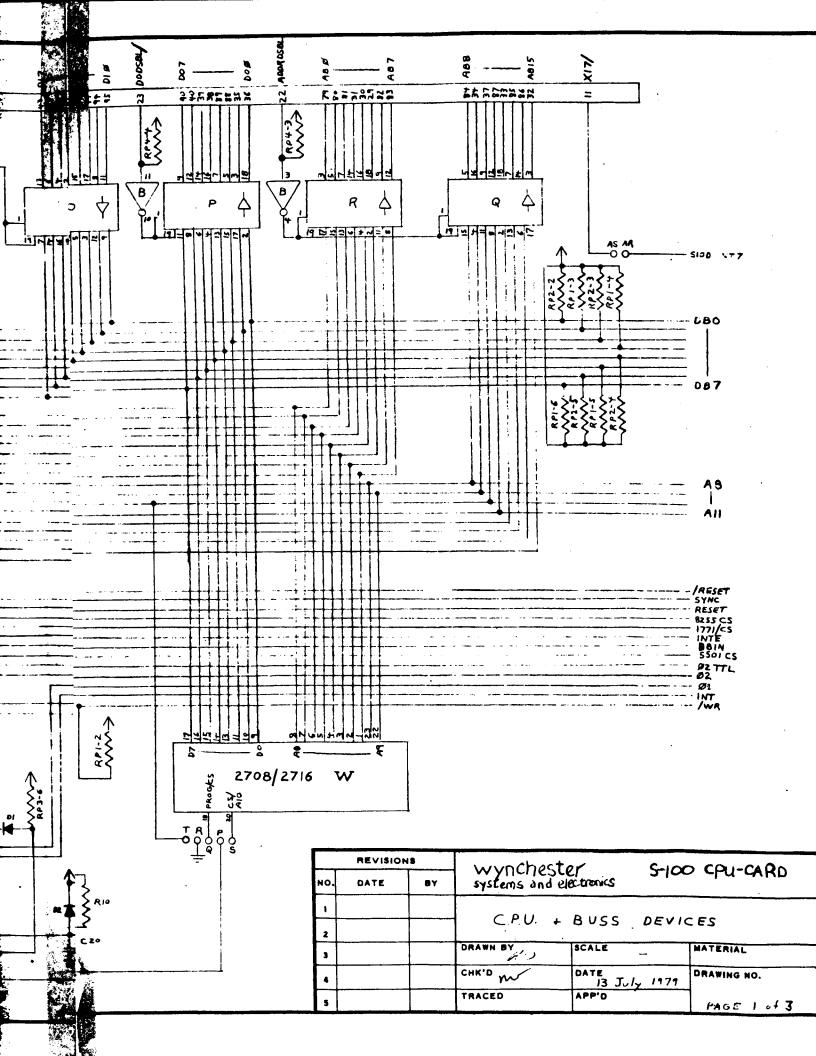

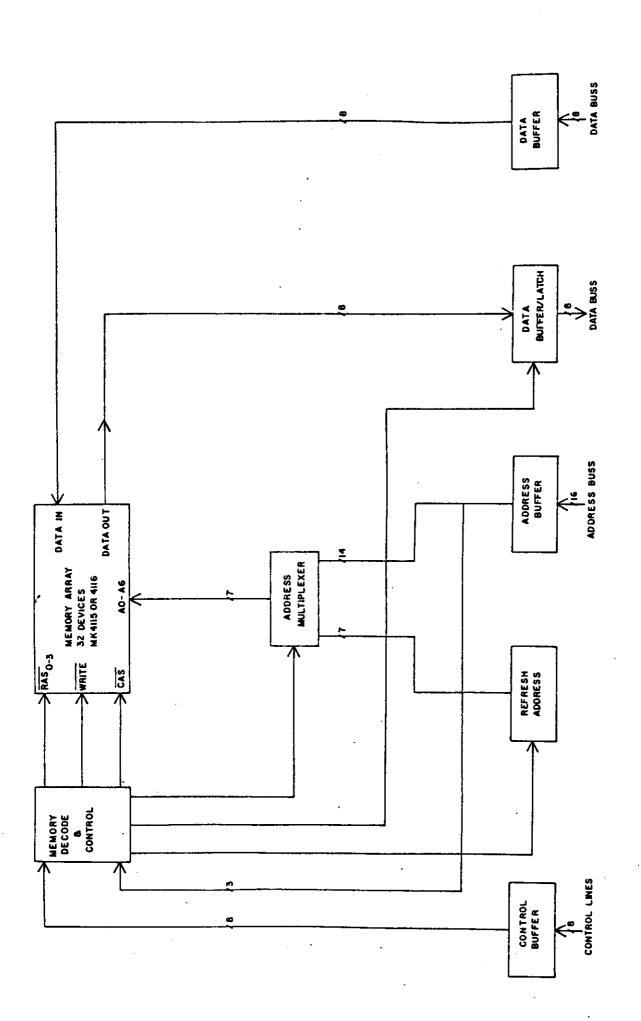

#### C.P.U.

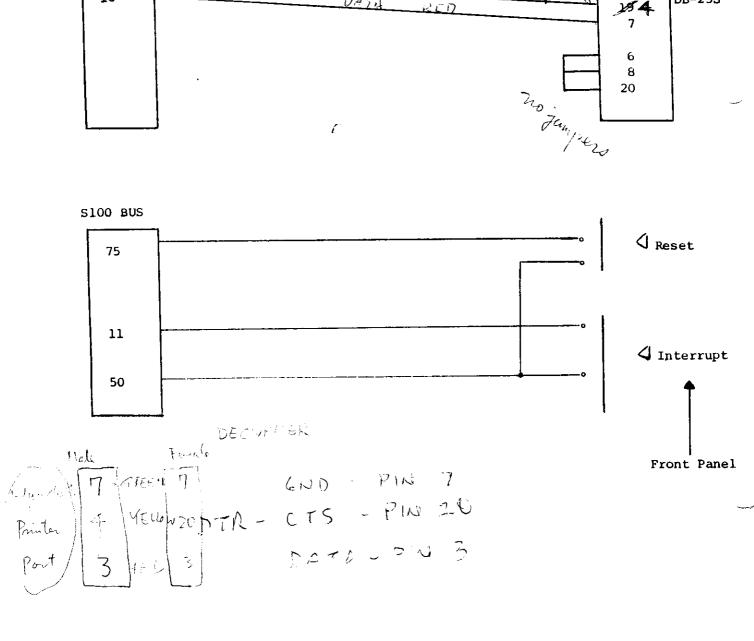

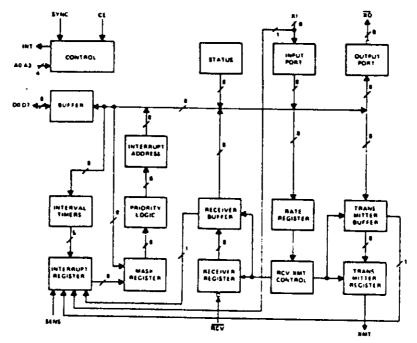

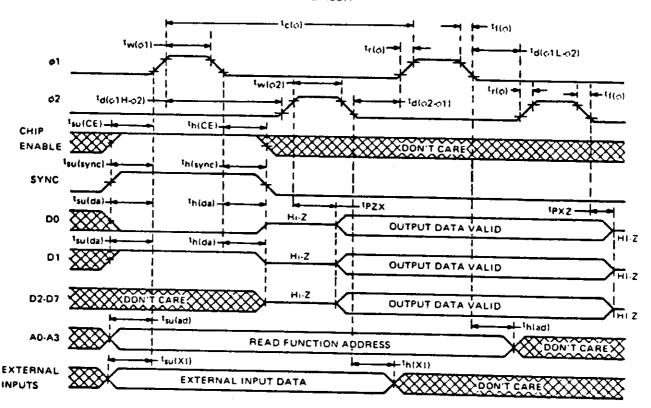

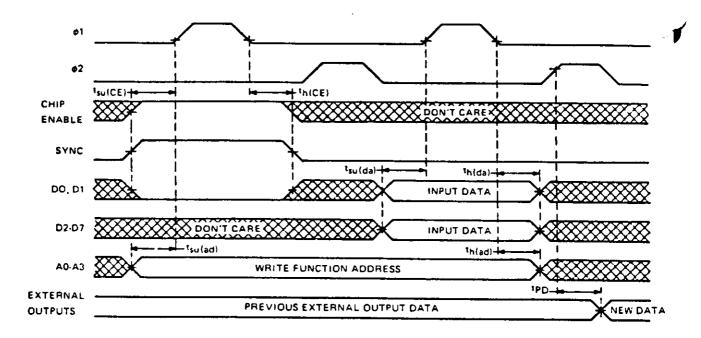

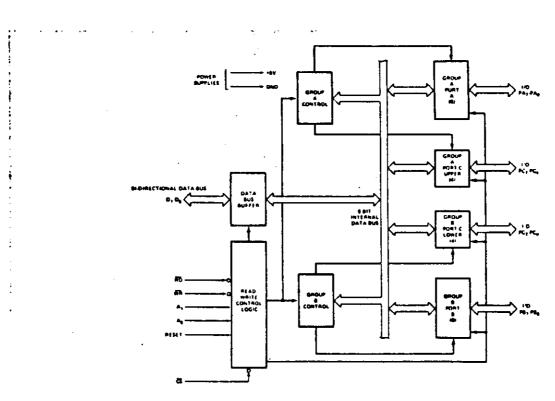

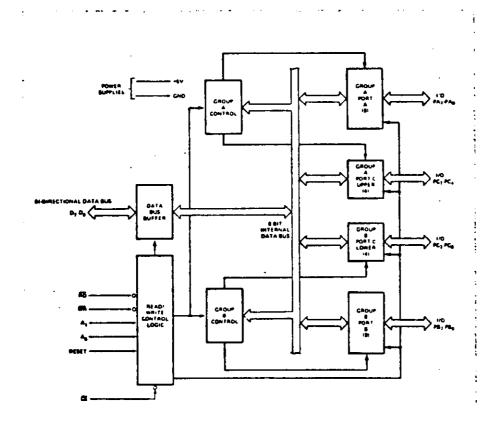

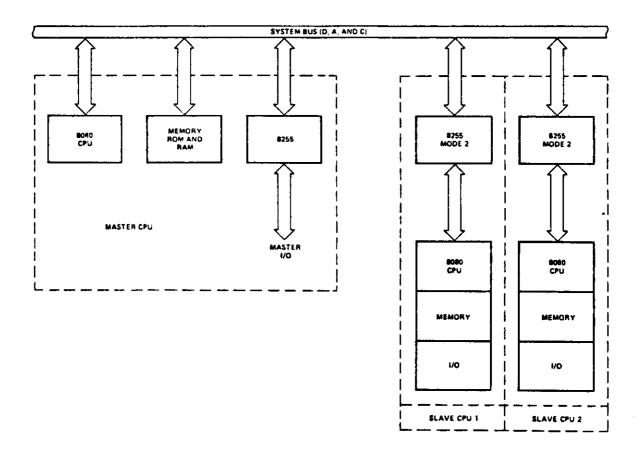

The WYNCHESTER central processor and input/output system provides all of the CPU and I/O facilities required for the W7993.

The single card has the following features:

- 2 Mhz. 8080A Microprocessor with fully buffered S-100 bus interface system.

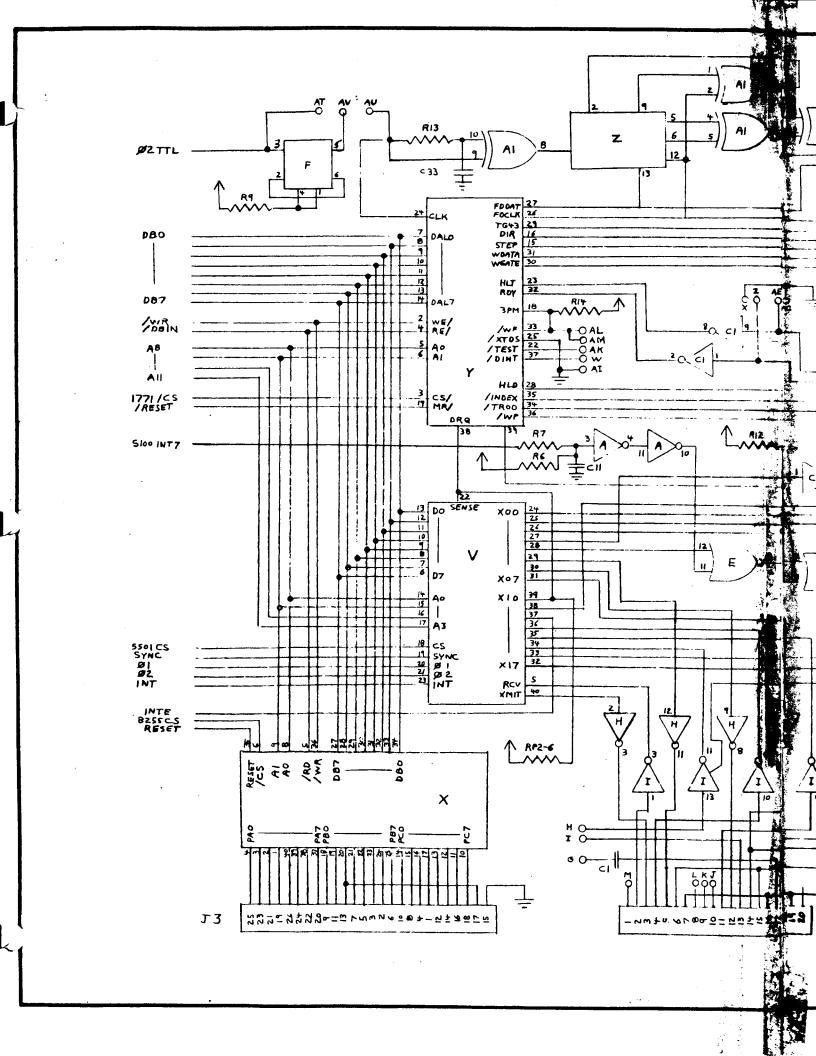

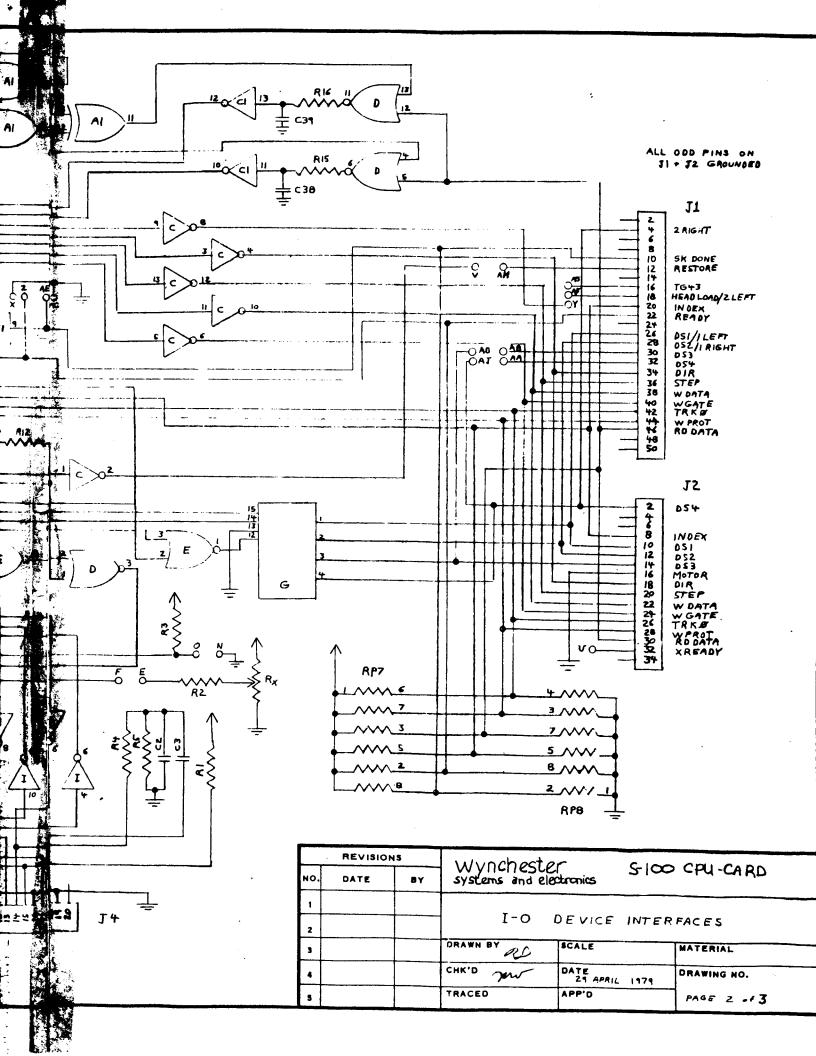

- EIA RS-232 compatible terminal port with software programmable baud rates from 110 baud to 76 kilobaud.

- Fully vectored interrupt system using TMS-5501 integrated circuit.

- Five programmable interval timers with interrupt capability using the TMS-5501 integrated circuit.

- An EIA compatible auxiliary pseudo-serial port suitable for interfacing with a serial printer at baud rates of up to 2400 baud.

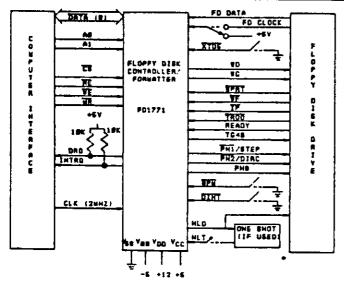

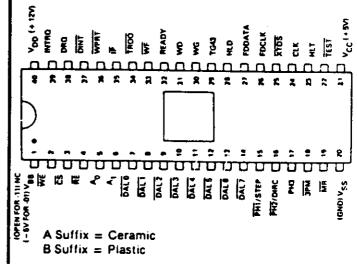

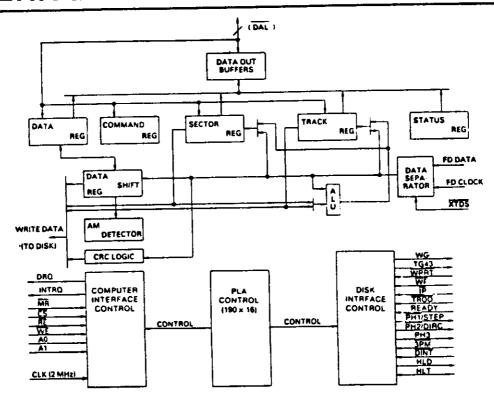

- An interface compatible with many common diskette and miniature diskette drives supporting IBM 3740 soft-sectored format.

- On-board digital data separator for full size diskette drives.

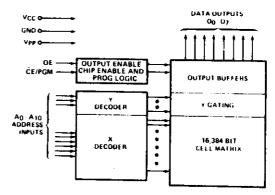

- Provision for up to 2K bytes of EPROM memory (2708 or 2716) with power on vectoring to allow page 0 to be left free for RAM (does not require memory cards with phantom option).

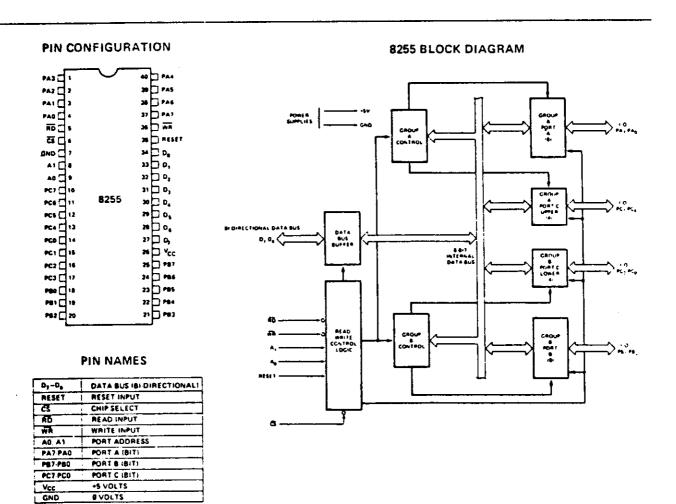

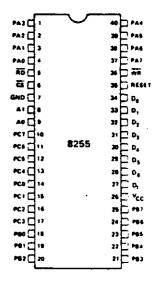

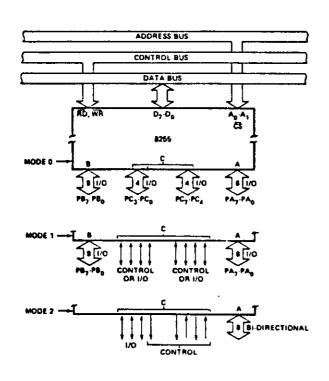

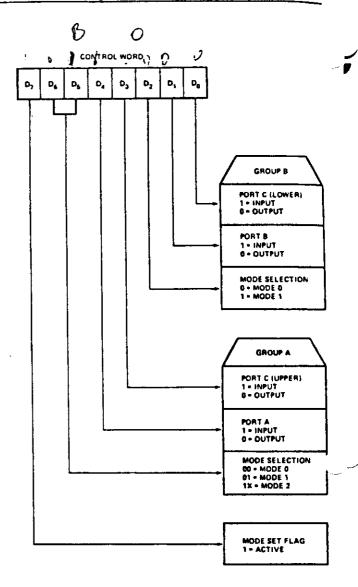

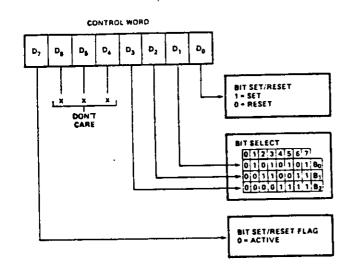

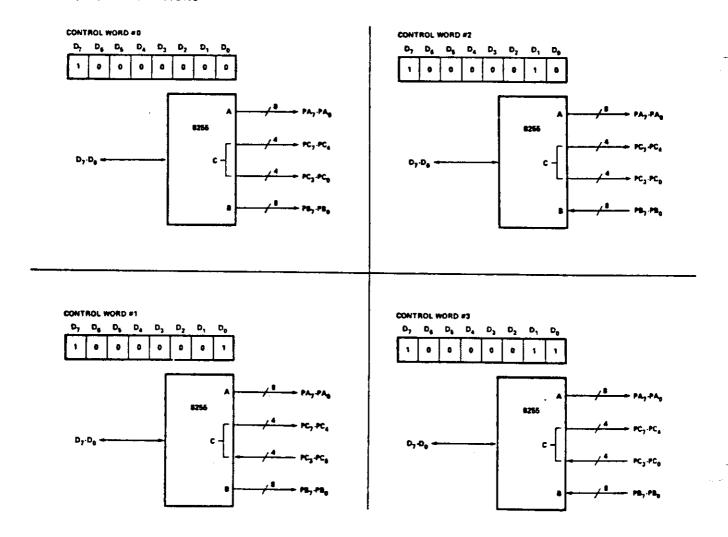

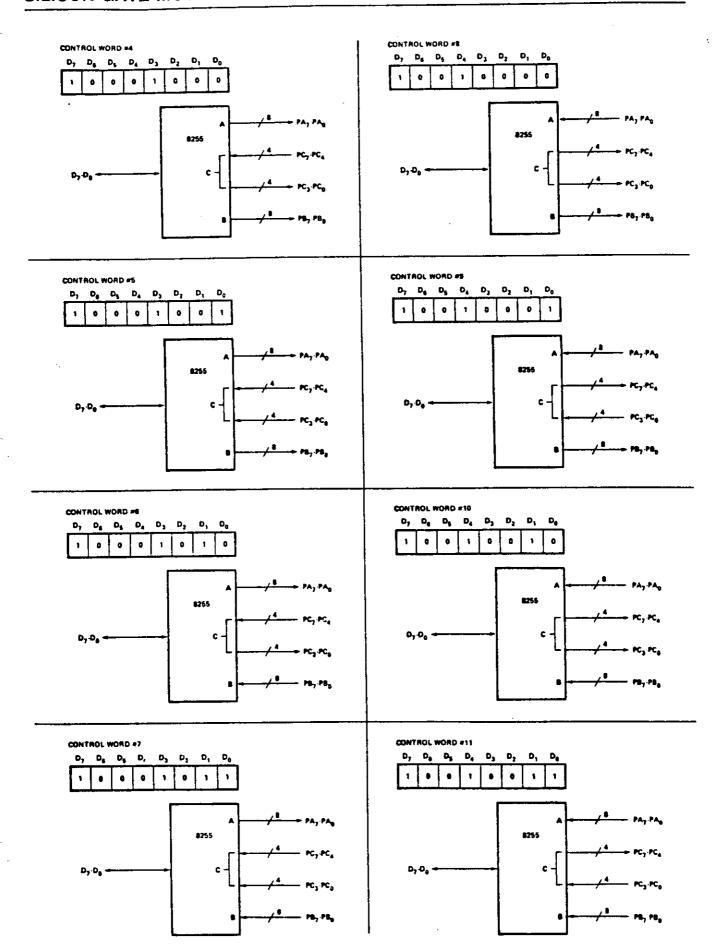

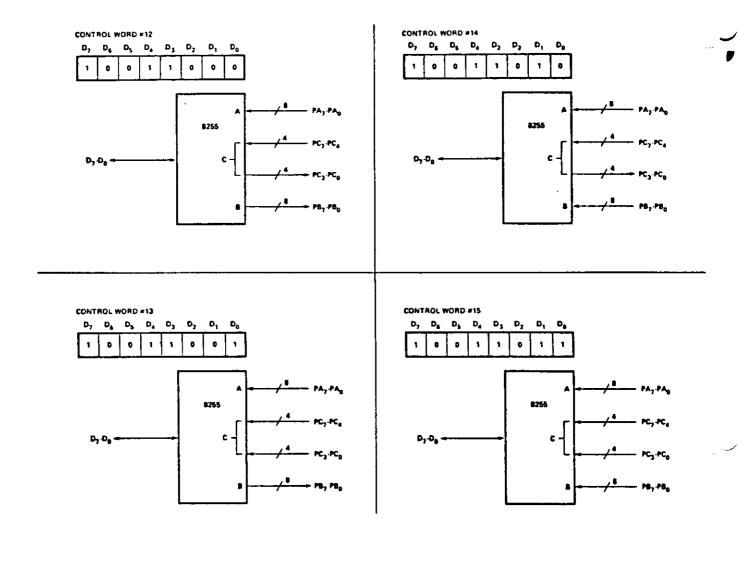

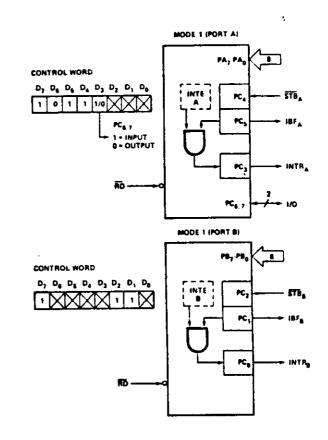

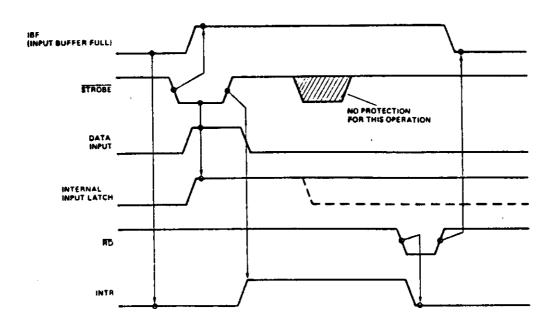

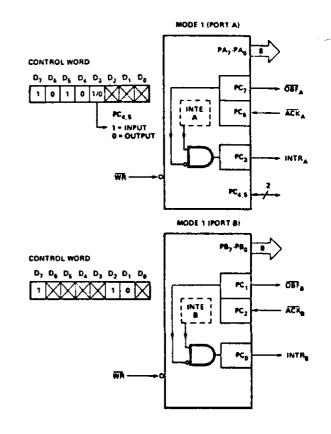

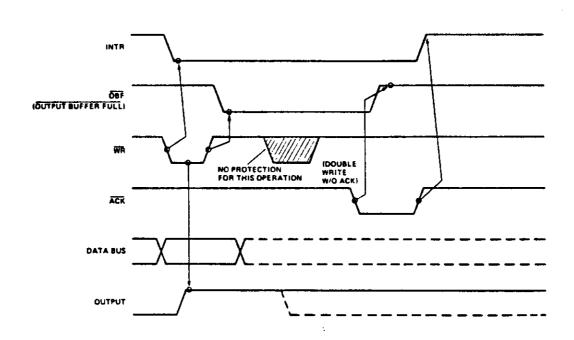

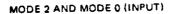

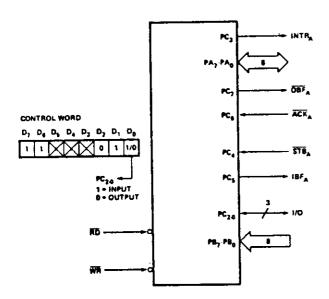

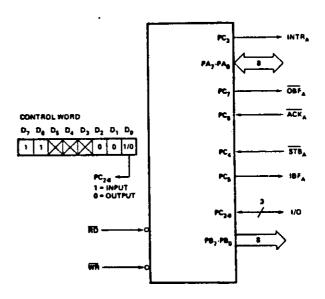

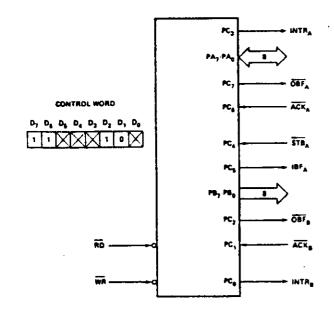

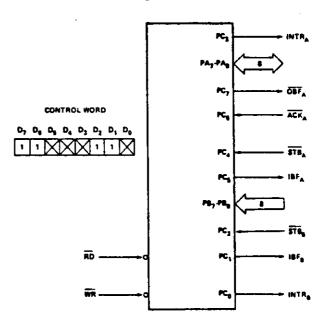

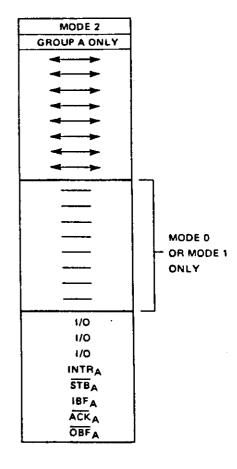

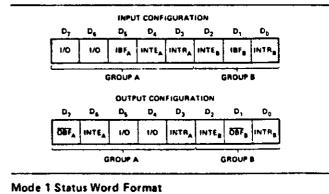

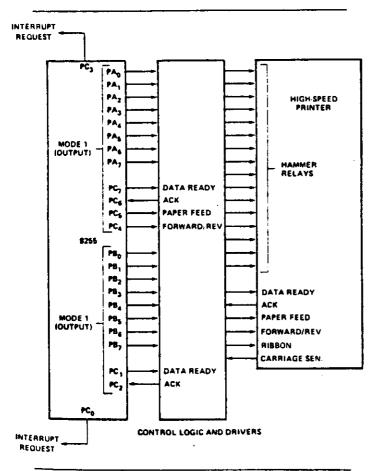

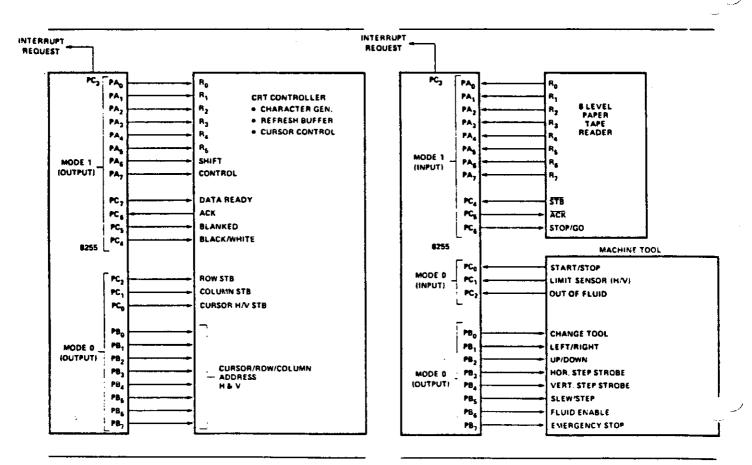

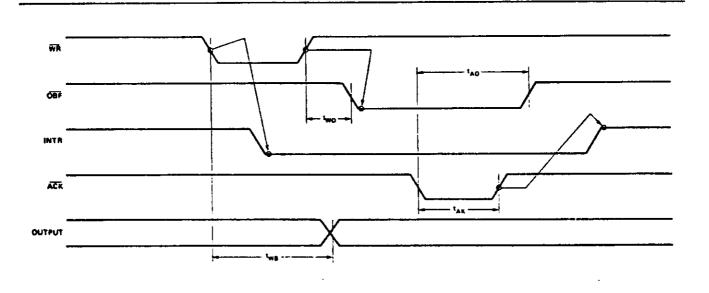

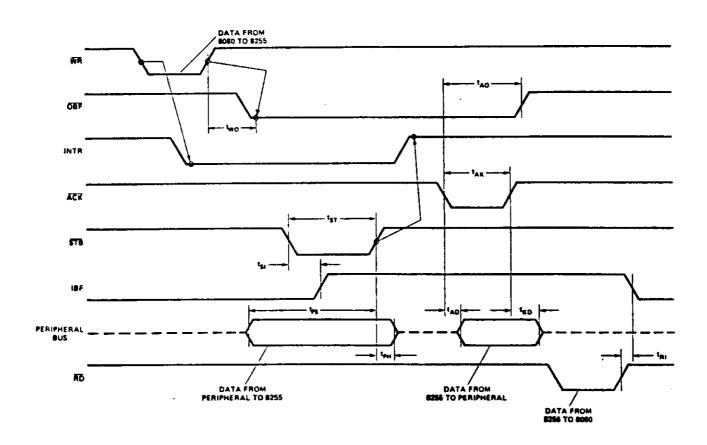

- 24 spare parallel user I/O lines with provisions for fully handshaked use as input or output ports (8255).

- Unique dual-mapped I/O interfacing allows optimal programming for I/O access. All devices may be accessed either in I/O space or as memory locations as the programmer desires.

- MWRITE generation on board so that no front panel is needed.

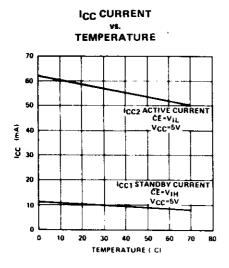

- Low power operation, typically requires 8V at 0.8A, 15V at 0.15A, and -15V at 0.05A

- Auxiliary cassette input and output (software driven) is available for use without disk in some stand alone applications.

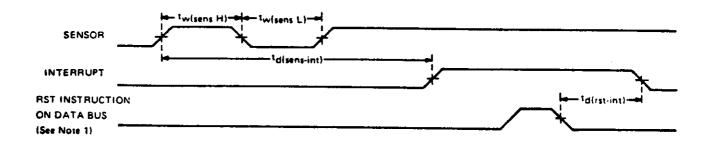

- The design accommodates an optional switch for generation of a user interrupt on level RST 7 for use with a debugger or user program.

Note that the second part of the program.

|   | · |  |   |             |

|---|---|--|---|-------------|

|   |   |  |   |             |

|   |   |  |   |             |

| • |   |  |   |             |

|   |   |  |   |             |

|   |   |  | , | · · · · · · |

|   |   |  |   |             |

|   |   |  |   |             |

# MEMORY MAP FOR CP/M OPERATION

| ffff        | *********        | ****                                                  | *****       |

|-------------|------------------|-------------------------------------------------------|-------------|

|             | top half of 2716 |                                                       |             |

| fc00        | **********       | ****                                                  | *****       |

|             | bottom half of 2 |                                                       |             |

| f800        | *********        | *****                                                 | ******      |

|             | 8255 PPI         | ctrl                                                  | f700-f7ff   |

|             |                  | C port                                                | f600-f6ff   |

|             | (user IO)        | B port                                                | f500-f5ff   |

| <b>7100</b> |                  | A port                                                | f400-f4ff   |

| £400        | ***********      | ******                                                |             |

|             | FD1771           | data                                                  | f300-f3ff   |

|             | diskette         | sector                                                | f200-f2ff   |

|             | controller       | track                                                 | f100-f1ff   |

| 5000        |                  | st/cmd                                                | f000-f0ff   |

| f000        | ********         | ******                                                | ******      |

|             | TMS5501          | none                                                  | ef00-efff   |

|             |                  | none                                                  | ee00-eeff   |

|             |                  | timer5                                                | ed00-edff   |

|             |                  | timer4                                                | ec00-ecff   |

|             |                  | timer3                                                | eb00-ebff   |

|             |                  | timer2                                                | ea00-eaff   |

|             |                  | timerl                                                | e900-e9ff   |

|             |                  | mask                                                  | e800-e8ff   |

|             |                  | par.out                                               | e700-e7ff   |

| •           |                  | tx buff                                               | e600-e6ff   |

|             |                  | baud                                                  | e500-e5ff   |

|             |                  | cmnd                                                  | e400-e4ff   |

|             |                  | stat                                                  | e300-e3ff   |

|             |                  | rst #                                                 | e200-e2ff   |

|             |                  | par.in                                                | e100-e1ff   |

| e000        |                  | rx in                                                 | e000-e0ff   |

| 6000        | **********       | *****                                                 | ******      |

|             | _                |                                                       |             |

|             | R                | AM BOARDS                                             |             |

| 07ff        | ****             |                                                       |             |