# THE PRO-80

ASSEMBLY

AND

OPERATIONS

MANUAL

PROTEC reserves the right to make changes at any time without notice to this publication and/or to the PRO-80 microcomputer. The information contained herein is believed to be accurate. However, PROTEC assures no responsibility for its user; nor any infrigements of patents or other rights of third parties which would result.

Copyright (c) 1981 by PROTEC. World rights reserved.

No part of this work may be reproduced, recorded or distributed in any form or by any means without the written permission of PROTEC.

On deposit at the National Library 3rd trimister, 1981.

# TABLE OF CONTENTS

| INTRO | OUCTION                                                                                                                                                                                                                                                   | . 1                                                                                                                                                                  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I. TI | PRO-80 ARCHITECTURE  1 Introduction.  2 The Z-80.  3 Memories.  1.3.1 Memory Mapping.  4 Port Decoding.  5 The Z80-PIO.  6 Keyboard Scanning and HEX Display.  7 Cassette Tape Interface.  8 Single Step.  9 Oscillator.  10 Power Supply.  11 S-100 BUS. |                                                                                                                                                                      |

| II.   | SEMBLY                                                                                                                                                                                                                                                    |                                                                                                                                                                      |

|       | 2.1 Introduction 2.2 Resistances 2.3 Capacitors 2.4 Integrated circuits 2.4.1 Integrated Circuit Mounting 2.5 Soldering 2.6 Assembly, 2.7 Preliminary Checking                                                                                            | 11<br>12<br>13<br>14<br>14<br>15                                                                                                                                     |

| III.  | HE MONITOR                                                                                                                                                                                                                                                |                                                                                                                                                                      |

|       |                                                                                                                                                                                                                                                           | 21<br>21<br>22<br>23<br>24<br>25<br>26<br>26<br>27<br>27<br>27<br>27<br>27<br>27<br>27<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30 |

|       | 3.9 Cassette Read                                                                                                                                                                                                                                         | J1<br>31                                                                                                                                                             |

# IV APPLICATION PROGRAMS

|      | 4.  | 2   | Chase<br>Traff<br>Digit | ic          | Ligh  | hts. |        |     |     |   |     |     | <br>  | ٠.     | ٠ | ٠. | • | <br>• | ٠. | ٠     | • | <br>35 |

|------|-----|-----|-------------------------|-------------|-------|------|--------|-----|-----|---|-----|-----|-------|--------|---|----|---|-------|----|-------|---|--------|

| ANNE | X 1 | . 1 | PRO-                    | -8 <b>o</b> | DIA   | GRAM | i • •, |     |     |   |     |     | <br>• | <br>٠. |   |    | • |       |    |       |   | <br>44 |

| ANNE | X 2 | 2 : | PRO-                    | -80         | MON   | ITOF | 2      |     |     |   |     | • • | <br>  | <br>٠. | • |    |   | <br>• |    | <br>• | • | <br>48 |

| ANNE | x 3 | 3 : | RST                     | "RJ         | ESTA. | RT'" | INS    | STF | ₹UC | T | [0] | Ν.  |       | <br>   |   |    |   |       |    |       |   | <br>63 |

#### INTRODUCTION

The Z-80 microprocessor has had a successful existance for 5 years. During this time the Z-80 has exceeded all hopes and expectations of the industry.

The powerful set of 158 basic instructions, (696 with the different addressing modes), the indexing capability and 16 bit arithmetic operation gives the Z-80 features that are found only in a minicomputer. The 8 addressing modes and 3 interupt modes combined with the block transfer instructions make the Z-80 a hard to beat 8-bit microprocessor. Furthermore, the 8080-A instruction set is a subset of Z-80 instructions. This permits programs written for 8080-A to be used directly with the Z80, allowing the user to choose from among the thousands of programs already available.

Manufacturers have lost no time in putting this powerful worker to the test. The microcomputers built around the

Z-80 and oriented toward the small and medium sized business

are multiplying with profusion, leaving a rather embarrassing

amount of choice to eventual users of this type of computer.

Meanwhile, there doesn't exist a truly economical and educational system that meets the needs of students, teachers,

experimenters or anyone who wishes to know or evaluate at a

reasonable price the performance of this wonderful machine,

the Z-80.

It is precisely this void that we wish to fill in offering the PRO-80, we have designed it with care for maximum versatility, we have given it a  $\tilde{S}$ -100 bus allowing the user to expand his system at will by choosing from various modules already available on the market. We have provided wire wrap space for experimentation and building process control circuits on the same prime circuit board. The PRO-80 also has two parrallel input/output ports (280-PIO) permitting access to external peripheral equipment. These two ports possess 3 bits each, and each bit can be controlled by software. These assure the user control of 16 individual lines for particular applications. The Z80-PIO also has an internal interupt control and two pairs of lines for external exchanges (handshake). An interface for an audio cassette recorder provides the user with an economical means of recording programs and data directly on minicassette tapes.

The PRO-80 memory is made of 1 Kbyte of RAM expandable on the board to 2 Kbytes. A third Kbyte of EPROM contains the monitor which performs several powerful functions such as memory examine and change, register examine and change, next memory location, next alternate register and a single

step operation mode, that provides you with the capability to execute and debug your program one instruction at a time. Other functions such as reset, program execute and cassette read-write are also featured on the PRO-80 monitor.

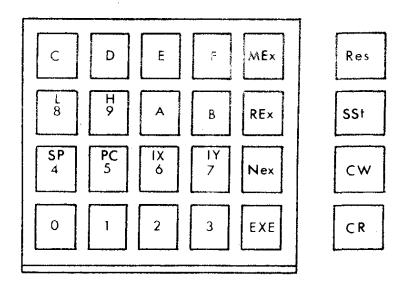

A hex keyboard, with 8 additional keys is used to load data and programs and to initiate the different functions of the monitor. Six "seven segment" digits are used to display the memory addresses, the Z-80 registers, the alternate registers and their contents.

The PRO-80 requires only a 5 volt, 1 ampere power supply. We have incorporated a 5V/1A voltage regulator so that only an 8 volt, 1 ampere transformer-rectifier is required to complete the PRO-80 power supply; this power pack is available through PROTEC.

Chapter 1 of this manual introduces the PRO-80 architecture. The basic components of the system are briefly described. Readers should however, have some background in microcomputers to fully understand the whole system design and operation. For beginners, this technical manual will be insufficient. Therefore, we refer them to a more detailed book, specially written for the Z-80, "Programming the Z-80" by Rodnay Zaks, Sybex.

Chapter II describes components such as resistors, capacitors and intergrated circuits. The beginner will learn to identify every component of the PRO-80. We have given all the instructions required for the assembly and testing of the PRO-80 microcomputer.

Chapter III describes the operation of the monitor. Every function of this program has been described, and several examples are given so as to better understand their mode of operation.

Chapter IV deals with three simulations: a light chaser, a traffic light and a digital clock.

# I The PRO-80 Architecture

# 1.1 Introduction

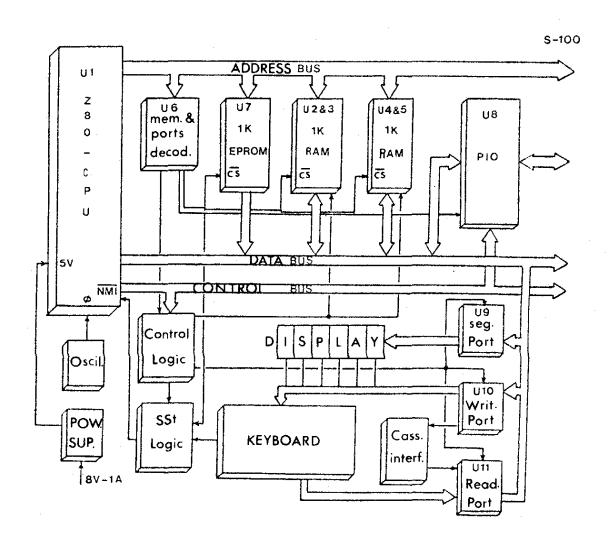

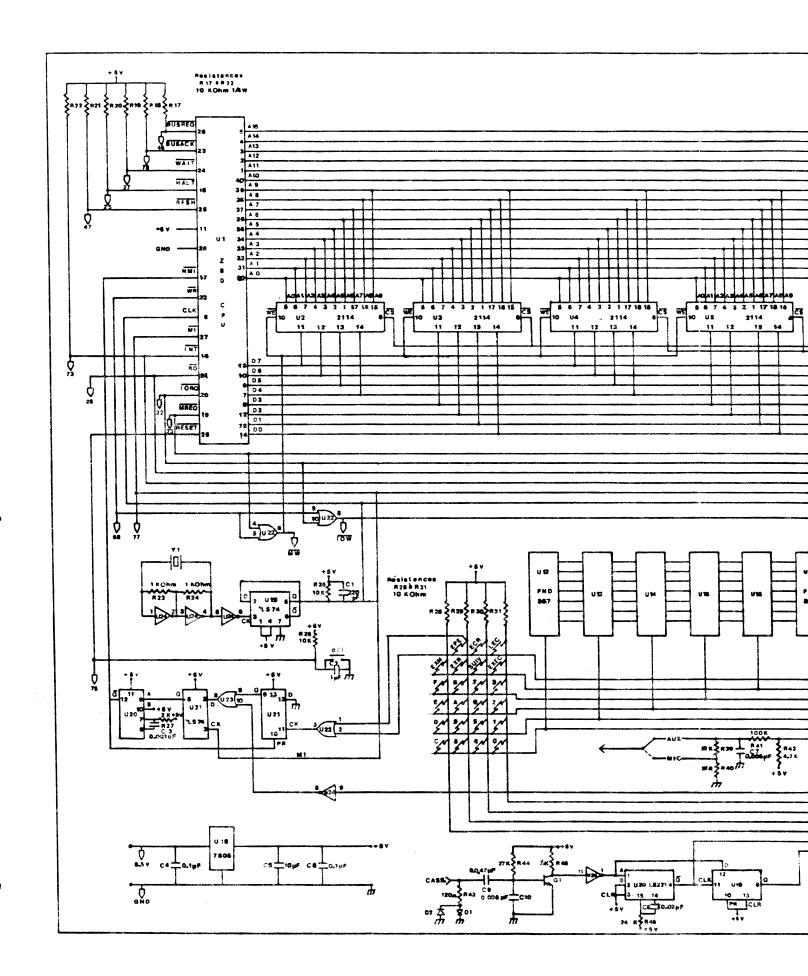

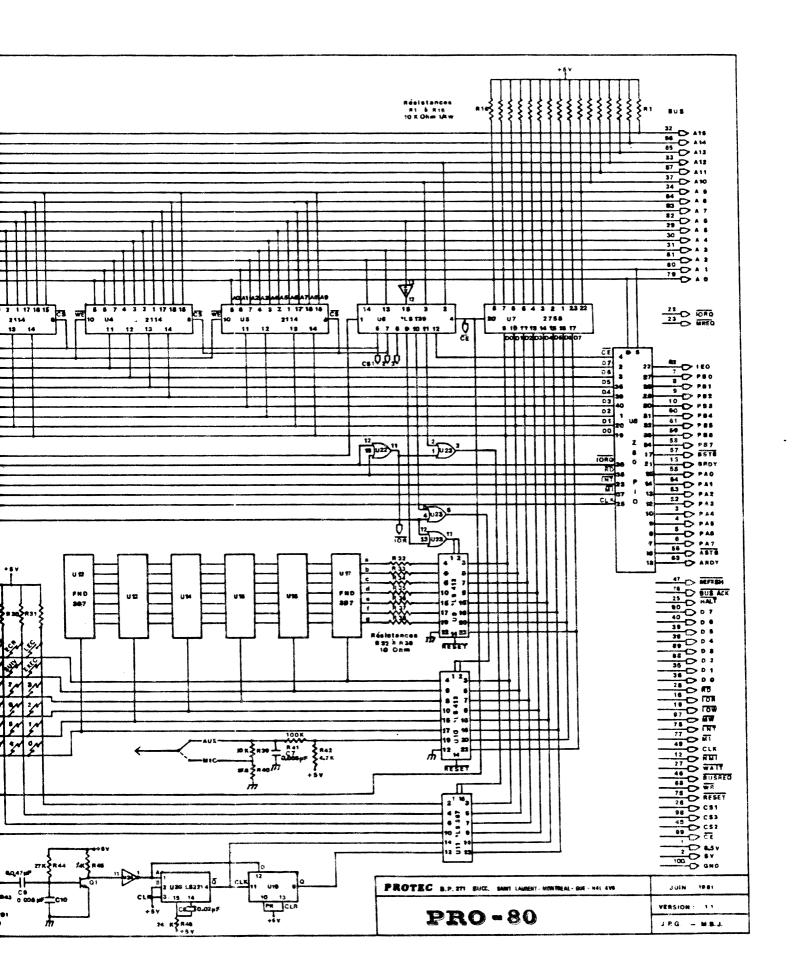

The complete electronic diagram of the PRO-80 is shown in Annex 1. A simplified version of this diagram is given in figure 1.1 which explains the functions carried out by the main components of the system.

Figure 1.1: The PRO-80 Architecture

# 1.2 The Z-80

This microprocessor is made up of nearly 8000 transistors and is the brain of the PRO-80. It is almost a microcomputer in itself, consisting of three main units: the arithmetic and logic unit (ALU), the control unit and the internal memory unit.

Depending on the instruction being processed, the ALU can execute logic operations such as and, or, exclusive or, shift left, shift right and so on... It can also execute arithmetic operations such as increments, additions, etc...

The control unit is the system's management center, It controls the various steps of the process. Depending on the system's status and the instructions sequence, this unit generates the right signals to access external memories, to route all necessary information to the ALU, to the various registers, or to manage exchanges with the peripherals.

The Z-80 internal memory unit is the only one that features 22 registers for a total memory capacity of 207 bits. These registers are used to store information generated by the CPU or by any external component. This memory features (\*):

- Two sets of identical 8-bit registers, each set consisting of an accumulator (A), a flag register (F) and three pairs of registers (B C, D E, H L) that can be used separatily or in pairs as 16-bit registers.

- An 8-bit interrupt register (I) which allows a minimal access time to a service routine in any memory location. In the interrupt mode, the I-register holds the high byte of the routine address. The low byte is generated by the peripheral requesting the interrupt.

- 7-bit register (R) is used to refresh the dynamic memories.

- Two 16-bit registers (IX and IY) are used for indexed addressing. In this addressing mode, the register (either IX or IY) contains a reference memory location. An additional byte included in the indexed instructions gives the offset relative to the reference address

- A stack pointer (SP), which holds a 16-bit address of the top stack located in an external system RAM memory. The stack operates in a "last in, first out" manner which allows the last information added to the stack (PUSHED) to be the first removed (POPED).

- (\*): See cover of the "Microreference Manual", Mostek.

- At last, the program counter (PC) which holds the 16-bit address of the current instruction being fetched from the memory.

Further information can be found in the "Z-80 CPU Technical Manual" by Mostek or Zilog.

#### 1.3. MEMORIES

Memories are made up of individual cells, capable of storing information. The memory capacity is expressed in binary digits called bits, or more often in bytes consisting of 8 bits. A 1 Kbyte memory consists of 210(i.e. 1024) bytes of 8 bits each.

There are two basic categories of memory. The first one is the read only memories (ROM) which stores information permanently: its content remaining always unaltered even when the electric power supply is shut off. The ROM content is wired in by the manufacturer. However, different kinds of ROM such as PROM and EPROM allow the user to pattern his own ROM. The PROM can be programmed by the user while the EPROM are erasable and reprogrammable, provided a special procedure is followed.

The second category of memory is the RAM (Random Access Memory) in which reading and writing operations are software controllable and information is randomly accessed. In this type of memory, information is lost when the electric power is shut off.

The PRO-80 has 1 Kbyte EPROM (U7) that holds the monitor program even when the power is shut off. A user 1 Kbyte RAM (U2 and U3) has been provided and allowance has been made for an extra Kbyte of RAM (U4 and U5).

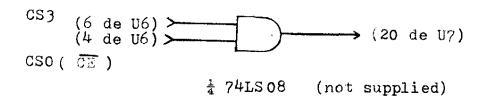

The more experienced reader can easily obtain an extra Kbyte of EPROM for his own personal use: Instead of grounding pin #19 of the 2716 chip (2 Kbyte EPROM), this pin should be connected to A-10. The following change would then be necessary to allow access to the second Kbyte of EPROM:

# 1.3.1 MEMORY MAPPING

Table 1.1 is a summary of a memory map. We can see with it that the monitor is located in the first Kbyte of memory (address locations 0000H(1)to03FF H. It also uses the last 122 bytes of the RAM (locations 1386H to 13FFH). Therefore, the programmer is not allowed access to these locations. The 0400H to OFFF addresses are not used by the system except when a second Kbyte of EPROM is made available. The user's RAM is located between 1000H and 1385H. Locations 1386 to 13BA are used for both user and monitor stack pointers. Locations 13BBH to 13CFH are used to route the RST instructions (see annex3). The optional Kbyte of RAM is located between 1400H and 17FFH.

| Locations      | Functions                  | Comments                                                         |

|----------------|----------------------------|------------------------------------------------------------------|

| 0000H to 03FFH | Monitor (U7)               | Executes the PRO-80 functions                                    |

| 0400H to OFFFH | Unused                     | Except when the second Kbyte of EPROM is made available (0400 to |

| 1000H to 1385H | RAM(U2-U3)                 | 07FFH).<br>User's memory area                                    |

| 1386H to 13AOH | User's stack<br>pointer    | RAM locations for user's stack                                   |

| 13AIH to 13BAH | Monitor's stack<br>pointer | RAM locations for monitor's stack                                |

| 13BBH to 13CFH | Monitor varia-<br>bles     | For more detail, refer to Annex 2                                |

| 1400H to 17FFH | RAM(U4-U5)                 | l optional Kbyte of RAM                                          |

| 1800н          | Unused                     |                                                                  |

Table 1.1: Memory Map List

(1):H: Hexadecimal.

This memory mapping requires an address decoder. This is carried out by the 74LS139 chip (U6) which also decodes the PRO-80 input/output ports.

# 1.4. PORT DECODING

In microcomputers, the information exchange between the CPU and its peripherals is handled by the input/output ports. Port addressing in the Z-80 requires 8 bits. This gives a possibility of 2 or 256 addressable ports. The PRO-80 uses 4 blocks consisting of 4 ports each detailed as below:

| Addresses  | I/O Ports            |

|------------|----------------------|

| 40H to 43H | PIO                  |

| 44H to 47H | Hexadecimal keyboard |

| 48H to 4BH | Display digits       |

| 4CH to 4FH | Display segments     |

Table 1.2: Input/output ports organization.

Keyboard reading, digit display and segment setting functions actually require only one port each. However, to simplify our design, we have dedicated 4 ports to each function, ports 44H to 47H therefore have exactly the same function, and either one can be used to initiate unit 11. The same applies to ports 48H to 4BH (U10) and to ports 4CH to 4FH (U9).

The PIO (Parallel Input/Output) however requires 4 separate ports. Their locations are given in the following paragraph.

#### 1.5. The Z80-PIO

The PIO has two input/output parallel ports (A&B), these ports are TTL compatible and can interface the PRO-80 with an ASCII keyboard, video monitor, card reader, printer and with a wide range of other peripherals. Each port has a control register that allows it to operate as an 8-bit input port or an 8-bit output port. Port A can also operate as an 8-bit bidirectional bus. Programming of such control registers is summarized on page 25 of the "Micro-Reference Manuel". Further information can be found in the Z-80-PIO Technical Manual" by Mostek/Zilog.

The PRO-80 input/output ports and control registers are decoded as shown below.

| ADDRESS LOCATION | PORTS              |

|------------------|--------------------|

| 40Н              | A Data Register    |

| <b>41</b> H      | B Data register    |

| 42H              | A Control Register |

| 43H              | B Control Register |

Figure 1.3: PIC port addressing

For more convenience, the data lines and "handshake" control signals have been connected to the S-100 bus on the FRO-80.

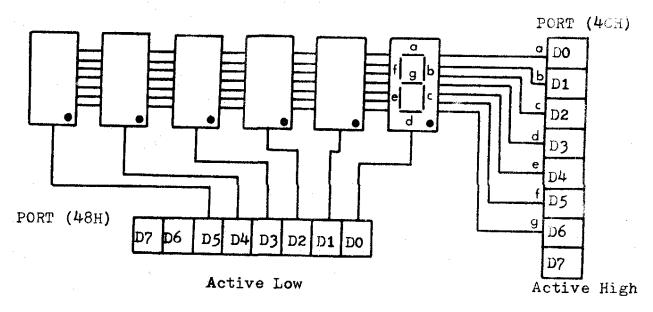

# 1.6. KEYBOARD SCANNING AND HEX DISPLAY

The PRO-80 monitor executes these 2 functions simultaneously. When the "RES" key is depressed, the monitor resets the RAM variables and starts the hex keyboard and display scanning.

Data is sent to the display via unit 9 (port 4CH). The common cathode of the digit to be lighted is reset via unit 10 (port 48H). The logical "O" received from this port is also applied to a keyboard row. The digit is held on for a while and the monitor takes a reading of port 44H (unit 11) to check if a key in that row is depressed. New data is sent to the next digit, the monitor takes another reading of port 44H and the keyboard/display scanning continues.

#### 1.7. CASSETTE TAPE INTERFACE

The audio frequencies recorded by a cassette tape are much lower than those used in microcomputers. To be recorded the information must be made audible before it can be applied to the microphone or auxiliary input of a cassette recorder. The PRO-80 uses a format similar to the Kansas City Standard for program recording. "1"s are coded by a 2400Hz signal,"0"s by a 1200Hz signal and the data rate is approximately 300 bauds. Each recorded byte contains one start bit and one stop bit (both are zeroes). A recording of null bytes serves as a program delimiter(a 10 second pause as leader and a 5 second pause as trailer). Programs are recorded serially via data line D6 of port 48H (pin #20 of UIO). The signal is applied to low pass filter for high frequency suppressing. A voltage divider allows the cassette recording through the mic or auxiliary input. The PRO-80 comes wired with an output which must be connected to the auxiliary input of the cassette recorder.

In order to use a mic input, the following changes must be done to the traces located under R41:

The cassette RAM transfer is done through the recorder's earphone output. The signal is squared by an amplifier inverter and then decoded by U2O and U19.

A second signal applied to pin #14 of U11 is used by the monitor for synchronization purposes during its serial to parrallel conversion.

#### 1.8 SINGLE STEP

This fonction is carried out by a special logic under the monitor control. It provides a powerful debugging tool, allowing the programmer to execute the program under development one instruction at a time. Depressing the "SST" key causes output "3" of U22 to go low. The falling edge of this signal is used to transfer a "0" to the output Q of U21 (input 9 of U23). As soon as the execution of an instruction contained in the RAM begins, "Œ" of the PROM becomes high. It is inverted by U24, and a "0" is applied to the second input of U23 (pin #10). The output of this gate then becomes low. At the falling edge of MI generated by the Z-80 during the fetch cycle, the "0" is transfered to the input A of the U20 flip-flop. This FF generates a pulse on the non-maskable interrupt of the Z-80 (NMI). As soon as the instruction has been executed, control returns to the monitor, the address of the next instruction and the accumulator content are displayed.

#### 1.9 OSCILLATOR

The clock signal that runs the Z-80 is generated by an oscillator using two inverters of U24. This oscillator is controlled by a 4MHz crystal. The output signal is divided by 2(U19) and applied to the Z-80 input clock.

#### 1.10 POWER SUPPLY

The 7805 (U18) built into the PRO-80, generates a regulated 5 Volts at 1 Amp. It needs only 7.5 to 8.5 Volts, 1 Amp. transformer rectifier and a 2200  $\mu F/16V$  electrolytic capacitor, to complete the Pro-80's power supply. Capacitors C4, C5,& C6 are used to maintain a more stable output voltage.

#### 1.11 S-100 BUS

Standardization has been sacrificed to increase flexibility so that almost all control signals used by the PRO-80 have been connected to the S-100 bus and are properlyidentified by a legend. The user can cut traces of unnecessary signals. He also can modify these signals in the wire wrap area, create other signals, connect them to the S-100 bus, etc... The Pro-80 offers maximum flexibility. The only limit is your imagination.

#### II ASSEMBLY

# 2.1. INTRODUCTION

Readers with some prior experience in the field of electronics may want to glance at the contents of the next four paragraphs. Others, however, should pay paticular attention to every detail given below. They can start to assemble the circuit only when each component has been identified.

#### 2.2. RESISTANCES

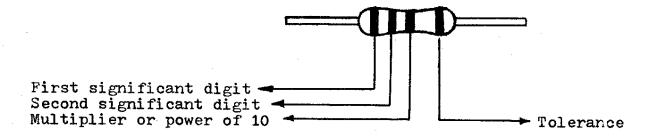

Resistances are defined by their value in ohms ( $\Omega$ ), Or in kiloohms ( $1K\Omega = 1000\Omega$ ) and by the tolerance relative to this value. Each resistance has different color bands to identify its value and tolerance (See figure 2.1)

Figure 2.1. Resistance value and tolerance code.

The first and second bands at the end of a resistance represent the first and second significant digits respectively, the third band indicates the multiplier factor(or power of 10); the fourth can be gold or silver and identifies the tolerance given to the resistance value. The following table lists the color code of resistances:

| COLOR          | SIGNIFICANT DIGIT                     | MULTIPLIER    | TOLERANCE   |

|----------------|---------------------------------------|---------------|-------------|

| black          | 0                                     | 1             |             |

| brown          | 1                                     | 10            |             |

| ${f red}$      | 2                                     | 100           |             |

| orange         | 3                                     | 1,000         | <u> </u>    |

| yellow         | 4                                     | 10,000        |             |

| gre <b>e</b> n | 5                                     | 100,000       |             |

| blue           | 6                                     | 1,000,000     |             |

| purple         | 7                                     | 10,000,000    | *********** |

| gray           | 8                                     | 100,000,000   |             |

| white          | 9                                     | 1,000,000,000 |             |

| gold           | · · · · · · · · · · · · · · · · · · · |               | 5%          |

| silver         |                                       |               | 10%         |

Example: The value of a resistance with yellow, violet, red and gold bands is:  $47 \times 100 n + 5\% = 47 \times 10^{2} n + 5\%$  or  $4.7 \text{ k}\Omega + 5\%$

# 2.3 CAPACITORS

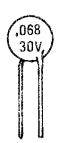

There are different types of capacitors. The PRO-80 kit includes a tantalum capacitor and several disc capacitors. (See figure2.2 for proper identification.)

Figure 2.2.: Capacitors used in the PRO-80 kit.

The value of disc capacitors is generally given with its maximum allowable voltage. This value can be expressed directly in micro Farads (µF)

0.068 µF capacitor, maximum 30 volts

It can also be expressed in pico Farads (pF), with two significant digits followed by a multiplier

Example

Capacity value of 47x10<sup>3</sup>pF= 47000pF = .047 jrF, 25 volts maximum.

Note:  $l\mu F = 1,000,000 pF$

#### 2.4. INTEGRATED CIRCUITS

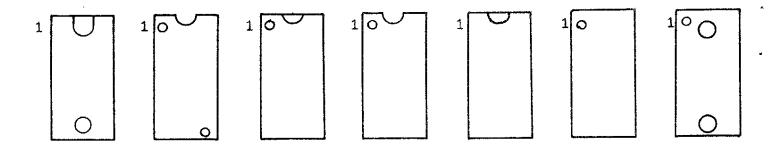

Integrated circuits do not all look alike. The most common type is called a DIP or "Dual In Line Package". DIP IC pins are numbered, so we must first identify pin #1 and by travelling counterclockwise determine pin numbers 2,3,etc... Several standards are used to iden tify pin #1. The following figure indicates most of these standards.

Figure 2.3.: Orientation of intergrated circuits

Note that it is essential to determine the correct position of integrated circuits before inserting them in their sockets. In the Pro-80, all IC's are placed so that pin #1 (identified by a white dot on the printed board) is at the upper left hand corner when the hex keyboard is at the lower right hand corner...

#### 2.4.1 INTEGRATED CIRCUIT MOUNTING

Integrated circuits usually come packaged with their rows of leads spread apart so that the space between the leads is slightly larger than the space between the socket holes in which the leads are to be inserted. Straighten the leads at 90° before inserting them into their socket holes. This must be done on a flat surface covered with a piece of aluminum foil (preferably grounded). IC pins such as those of the 2716, 2114, Z-80 CPU or Z-80-PIO should never be touched, otherwise these IC's would be damaged.

### 2.5. SOLDERING

Up to 90% of the defects are due to a bad soldering joint. The job must be done perfectly. We suggest that beginners practice with pieces of wire before trying their skills on the PRO-80 components.

Use a lead and tin solder (60/40 ratio), 20 or 22 guage. NEVER use an acid solder, it will corrode and rapidly damage printed circuits rendering the system inoperative.

The soldering iron must not be a heavy duty type: a 30 to 40 watt iron is enough for electronic soldering. The iron must be kept clean by wiping its tip with a damp sponge or cloth.

Components must be rid of all foreign matter before soldering. Place the tip of the iron on the spot where the wire and printed circuit meet. The tip must rest firmly on both elements. Apply the solder and watch carefully: the iron must be removed as soon as the compound starts to spread around the connection. Too much soldering can bridge two traces of printed circuits. Remove the iron and check the connection. It must be shaped like a funnel, be smooth and shiny. A "cold solder" looks rather dull and is often due to insufficient heat.

On the other hand, too much heat may damage the components and the board. Try to find a happy medium. The iron should be applied no more than two or three seconds. After each soldering, cut the excess wire as close as possible to the connection and start over for the next connection.

# 2.6. ASSEMBLY

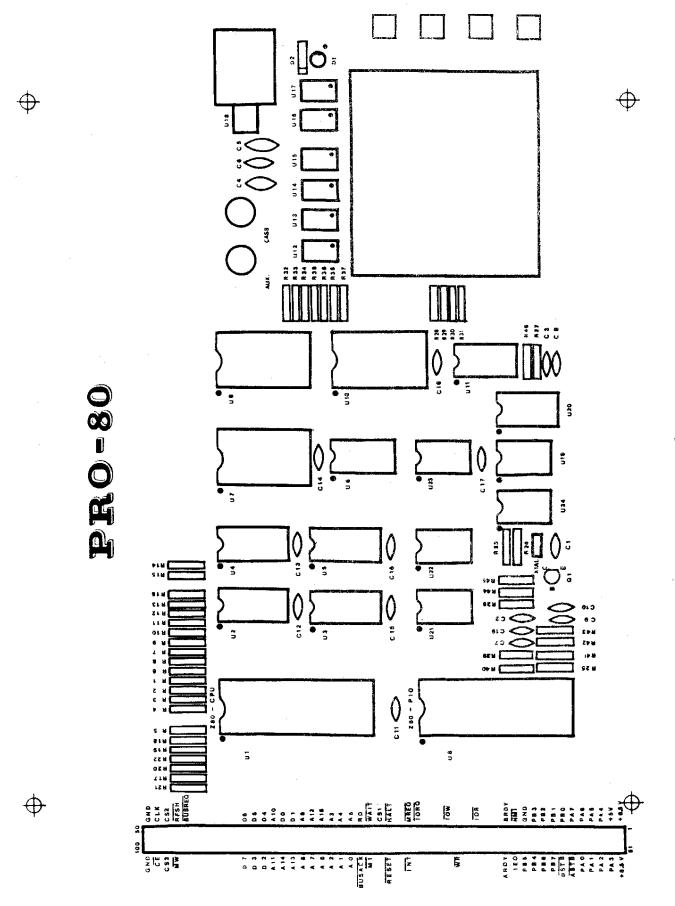

Consult your layout and parts list to identify each PRO-80 component. Get your iron and follow these directions:

- 1. Each north-south end of the printed board has three holes in which to insert the feet of the PRO-80; tighten the screws finger tight.

- 2. Mount and solder the following resistances:

- a- 10K, ½W, 5% (Brown-Black-Orange) .R14, R15, R16, R13, R12, R11, R10, R9, R7, R8, R6, R1, R2, R3, R4, R5, R18, R19, R22, R20, R17, R21

- b- R28, R29, R30, R31, R25, R26, R39

- c- 10, ½W, 5% (Brown-Black-Black) .R32, R33, R34, R38, R36, R35, R37.

- d- 1K, ½W, 5% (Brown-Black-Red) .R23, R24, R40

- e- 2K, ¼W, 5% (Red-Black-Red) .R27.R45

- f- 24K,  $\frac{1}{4}$ W, 5% (Red-Yellow-Orange) .R46

- g- 27K,  $\frac{1}{4}$ W, 5% (Red-Purple-Orange) .R44

- h- 100K,  $\frac{1}{4}$ W, 5% (Brown-Black-Yellow) .R41

- i-4.7K,  $\frac{1}{4}$ W, 5% (Yellow-Purple-Red) .R42

- j- 120, ¼W, 5% (Brown-Red-Brown) .R43

Figure 2.5 : PRO-80 LAYOUT

PARTS LIST

| LABEL                                                                                                                                                                                        | QUANTITY                                     | DESIGNATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | COMMENTS                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| U1 U2, U3 U6 U7 U8 U9,U10 U11 U12-U17 U18 U19,U21 U20 U22,U23 U24 Q1 R1-22,25,26, 28-31,39 R23,24,40, R27,R45 R32-R38 R41 R42 R43 R44 R46 C1 C2 C3 C5 C7, C10 C8 C9 C4,C6,C11-C19 XTAL D1 D2 | 121112161212119 3271111111112111111234351426 | Z-80 CPU 2114 74LS139 2716 (or 2516) Z-80 PIO 74S412 74LS367 FND367 7805 74LS74 74LS32 74LS32 74LS04 2N3904 Resistances1K Resistances2K " 10 " 100K " 4.7K " 120 " 27K " 24K Capacitor 22opF " 0.47uF " 0.001uF " 22 ur " 0.005uF " 0.02uF " 0.047uF " 0.047uF Crystal TIL 220 1N914 40 pins socket 14 pins socket 15 pins socket 16 pins socket 16 pins socket 17 pins socket 18 pins socket 19 pins socket 19 pins socket 19 pins socket 10 pins socket 11 pins socket 12 pins socket 13 pins socket 14 pins socket 15 pins socket 16 pins socket 17 pins socket 18 pins socket 19 pins socket 19 pins socket 19 pins socket 10 pins socket 11 pins socket 12 pins socket 13 pins socket 14 pins socket 15 pins socket 16 pins socket 17 pins socket 18 pins socket 19 pins socket 19 pins socket 19 pins socket 10 pins socket 11 pins socket 11 pins socket 12 pins socket 13 pins socket 14 pins socket 15 pins socket 16 pins socket 17 pins socket 18 pins socket 19 pins socket 19 pins socket 19 pins socket 10 pins socket 11 pins socket 11 pins socket 12 pins socket 13 pins socket 14 pins socket | Tantalum Ceramic(or 0.0047) Ceramic Ceramic Ceramic 4Mhz Light emitting diode Switching diode |

3. Mount and solder the following IC chip sockets:

```

a- 14 pins : U21-U22-U23-U24-U19

```

b- 16 pins : U6-U11-U20

c- 18 pins : U2-U3-U4-U5

d- 24 pins : U7-U9-U10 e- 40 pins : U1-U8

4. Mount and solder the 7 segment digits as follows UP

- 5. Mount and solder the D2 diode (band on left hand side) and the D1 LED the groove must be oriented towards the white dot on the printed circuit

- 6. Mount and solder the following capacitors:

a- 0.1µF : C4, C6, C11, C12, C13, C14, C15, C16, C17, C18, C19

b- 220pF : C1

c- 0.47µF : C2

d- 0.001µF : C3 e- 22 µF : C5, the red dot must be placed <u>downwards</u>.

f- 0.005µF : C7, C10

g- 0.02µF : C8

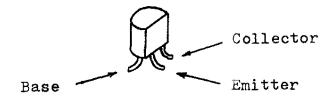

7. Mount and solder the XTAL crystal and Q1 transistor. The transistor should be placed as indicated below:

- 8. Mount and solder the U18 regulator.

- 9. Mount and solder the four push button keys.

10. Before mounting the keyboard, carefully straighten its pins placing them so that they appear on the flip side of the board, then apply enough solder to secure the connection.

Identify each key as in figure 2.6.

Figure 2.6 : Keyboard Layout

11. Mount and solder the audio connectors as illustrated in the figure below.

BOTTOM VIEW

Figure 2.7 : Audio Connectors Mounting.

12. If the second Kbyte of EPROM is not used, ground pin #19 of U7. (Solder bridge pins #19 & 20 of U7)

# 2.7. PRELIMINARY CHECKING

Connect an 8 volt, 1 ampere D.C. supply to the two feeding points in the upper right hand corner of the PRO-80. Please check the polarity (the + is up and the - is down). If you use the PROTEC power supply pack, the white wire must be connected to the +8 volts. When the power supply is connected, the third pin of U18 (display digit side) must be at +5V relative to its middle pin (ground). If that is not the case, check the solder joints and make sure there is no short circuits. DO NOT proceed to the next step before obtaining the required voltage.

Shut off the power supply and mount the integrated circuits observing the proper orientation (pin #1 on the same side as the white dot on the board).

| _ | U2-U3   | 3    |       |       |         |           | <br> | 2114           |    |

|---|---------|------|-------|-------|---------|-----------|------|----------------|----|

|   | 116     |      |       |       |         |           | <br> |                |    |

| _ | 1110-1  | 121  |       |       |         |           | <br> | 74LS74         |    |

| - | U22-U   | 123. |       | • • • | • • • • | • • • • • | <br> | 74LS <b>32</b> |    |

| - | U24.    |      | • • • | • • • | • • • • | • • • • • | <br> | 74LS04         |    |

|   | 1111    |      |       |       |         |           | <br> |                |    |

|   | 774 A T | T^   |       |       |         |           |      |                | ٠, |

| _ | 117     |      |       |       |         |           | <br> |                | )) |

| _ | 111     |      |       |       |         |           | <br> |                |    |

| - | U8      |      |       |       |         |           | <br> | z-80 PIO       |    |

Double check the orientation of the integrated circuits and make sure all pins fit securely in their holes.

The PRO-80 is now ready. Turn it on and depress the Res Push button. The " " prompt symbol must appear in the first leftmost digit position.

Everything is in order. Perfect ! Proceed to the next chapter.

If the " " " prompt symbol does not appear, shut off the power and double check the connections. Unwanted bridges, cold solder joints and overlooked connections are often to blame.

If you can't find any fault in the connections and if you don't have the proper troubleshooting equipment, contact your dealer or write to PROTEC at:

B.O. 271 St-Laurent Branch, Montreal (Quebec) Canada. H4L 4V6

#### III THE MONITOR

#### 3.1. INTRODUCTION

If the microprocessor is the brain of any microcomputer, the monitor program is its heart. Without a heart, the brain cannot function on its own. The monitor complexity may vary, but this program is always there to decode and manage the input/output transfer, and to help the programmer to load and debug his program. The PRO-80 monitor is stored in a non-volatile 1 kilobyte memory and allows the programmer to have a complete control over every function as further discussed below.

#### 3.2. THE RES PUSH BUTTON KEY

When this key is depressed, the processor is reset and the program execution begins at the first starting address 0000H. The PRO-80 monitor is located in the first kilobyte of the system's memory, so the 0000H address contains its first executable instruction. Depressing the RES key will cause the execution of the monitor program. The monitor initiates the user's stack pointer to address location 13A0H, resets the RAM variables and enters the MEMORY EXAMINE MODE. The system displays the " " " prompt symbol and starts scanning the keyboard for any new user entry.

#### 3.3 MEMORY EXAMINE

This function is used to enter a new program or to examine and change the content of a memory location. The memory examine mode is used as below:

- . Depress the MEX key. The monitor responds by displaying the " " prompt symbol.

- . Key in the four hex digit memory address (high digit first).

- . Depress the NEX key. The content of that memory location is displayed in the two data digit positions.

If the NEX key is depressed before the four address digits have been entered, no data is displayed and the monitor waits for the remaining address digits.

Displayed data can be changed simply by keying in new data and depressing the NEX key. This key causes the monitor to update the content of the memory location. The address is incremented by one and the content of this new location is displayed.

#### IMPORTANT:

When the PRO-80 has a one kilobyte RAM, the user's memory is located between 1000H and 1385H. (Consult the memory map list)

# 3.3.1. APPLICATION

Connect the PRO-80 to an +8 Volt, 1 ampere power supply and depress the following keys:

| uopi oli      | 3 ,         | ·                                                                                                                                                                                                                      |

|---------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - RES         |             |                                                                                                                                                                                                                        |

| -110          | 1 1 0       |                                                                                                                                                                                                                        |

| -14 <b>EX</b> | 1 1 0       | Incomplete address: nothing happens. the monitor waits for the fourth digit.                                                                                                                                           |

| - O           | 1 1 0 0     |                                                                                                                                                                                                                        |

| - NEX         | 1 1 0 0 X X | The two digits XX represent the content of memory address location 1100H. Change by keying in a new data. EX: 12H                                                                                                      |

| - 1           | 1 1 0 0 1 X |                                                                                                                                                                                                                        |

| - 2           | 1 1 0 0 1 2 | 12H is displayed but the location 1100H is updated by the monitor only when the NEX key is depressed. In case of error, new data cambe keyed in as many times as necessary. Depressing the NEX key validates the data. |

| - NEX         | 1 1 0 1 X X | 12H data is transferred to 1100H location. The memory address is incremented and the content of new address is displayed                                                                                               |

| - MEX         |             | Return to memory examine mode.                                                                                                                                                                                         |

| - 1100        | 1 1 0 0     |                                                                                                                                                                                                                        |

1 1 0 0 1 2

The new content of the memory location is displayed.

The procedure is simple and will be easily remembered if you try it out two or three times with your own data.

# 3.4. REGISTER EXAMINE

NEX

The PRO-80 uses an image register for each Z-80 register accessed by this function. The monitor transfers the content of the image registers to the microprocessor corresponding registers before each program execution, or single step execution. Conversely, the content of the Z-80 registers is retransmitted by the monitor to the image registers after each instruction is executed in the SINGLE STEP mode. This enables the user to:

- 1. Load a register before a program execute.

- 2. Examine or change during an execution in the single step mode, the content of the 8-bit registers A,B,C,D,E,F, and their corresponding alternate registers; the content of the 16-bit registers IX and IY, as well as those the program counter PC and the stack pointer SP. The procedure is described in the following paragraphs:

# 3.4.1. 8-BIT REGISTERS

- . Depressing REX key initiates the register examine mode. The letter " r " appears in the high address digit display.

- . Key in the desired register.

- . Depress the NEX key. The content of the register is displayed in the two data digit positions.

- . To modify the content, key in the new data and depress the NEX key.

- The monitor updates the content, displays the alternate registers and its content with the letter A (alternate) in the Low address position.

- . The same basic steps apply to change the alternate register content.

- . The NEX key initiates a new cycle which begins with the starting register.

- Repeat by depressing the REX key to examine or change the content of other registers or alternate registers.

#### 3.4.2 APPLICATION

The purpose of this exercise is to examine and change the contents of registers A and alternate A, and to check their new contents which will be IAH and 3EH respectively.

| - REX        | r       | Register examine mode                                                                                   |

|--------------|---------|---------------------------------------------------------------------------------------------------------|

| - A          | A       | Selected register                                                                                       |

| - NEX        | A X X   | $(A)^{(1)} = XX$                                                                                        |

| <b>- 1</b> A | A 1 A   | The new content of A is displayed but is not yet recorded in the image re-                              |

| - NEX        | A A X X | gister.  The content of A is now 1AH; the alternate A register is automatically displayed with its con- |

| - 3E         | A A 3 E | The content of A' is not yet updated: new data can be keyed in to correct any error.                    |

| - NEX        | A 1 A   | Uptade of (A'),(A)=1A                                                                                   |

| - NEX        | A A 3 E | (A')=3E                                                                                                 |

| _ REX        | r       | Return to the REX to exa-<br>mine or change the content<br>of another register.                         |

#### NOTES:

- 1. The prime mark "'" indicates the alternate register.

- 2. It is important to remember that the monitor makes changes on the image registers, and a program execute or single step execute is required for effective changes in the microprocessor registers.

- (1) the brackets denote the content of register(or memory location).

# 3.4.3 16-BIT REGISTERS

The same basic steps apply. The only difference is that the content of these registers is expressed by 4 hexadecimal digits. Use the following procedures:

- . Depress the REX key.

- . Key in the desired register.

- . Depress the NEX key. The monitor displays the high byte of the register's content. This byte can be changedusing the procedure described above for the 8-bit register.

- Depressing the NEX key again causes the monitor to update the high byte and to display the low byte with the "\_\_" identification symbol.

- . Data is modified following the same procedure.

- . Depressing the NEX key a third time causes the low byte to be updated and the high byte to be displayed. The cycle is repeated.

- . Depress the REX key and repeat the same procedure to examine or change the content of other registers.

# 3.4.4. APPLICATION

The purpose of the exercise is to examine and change the content of the program counter (PC) and to check its new content. We will be changing the content to 1000H.

| - REX    | r       | Examine register mode                                      |

|----------|---------|------------------------------------------------------------|

| - PC (5) | 5       | Selected register                                          |

| - NEX    | 5 X X   | The high byte in the PC is XX.                             |

| - 10     | 5 1 0   | The new byte is displayed but is still not recorded.       |

| - NEX    | 5 - X X | The high byte has been updated and the low byte is         |

| - 00     | 5 - 0 0 | displayed  The new value of the low byte is now displayed. |

|          |         |                                                            |

| _ | NEX | 5 | 1 0   |

|---|-----|---|-------|

| _ | NEX | 5 | - 0 0 |

| - | EXR | r |       |

The low byte is updated and the high byte is displayed with its new content.

The new value of the low byte is 00H.

Return to the REX mode to examine and change another register.

#### 3.5 NEXT MODE

This function is used in the REX mode and the MEX mode. The basic steps have already been explained in paragraphs 3 and 4 and are summarized below.

#### 3.5.1. MEX MODE

- . Depressing the NEX key causes the content of a memory address to be displayed

- . When the NEX key is depressed a second time, the monitor executes the following operations:

- It updates the content of the addressed memory location.

- It increments the address.

- It displays the incremented address with its content

#### 3.5.2 REX MODE

# 3.5.2.1. 8-BIT REGISTERS :

- . Depressing the NEX key causes the content of the register to be displayed.

- . When the NEX key is depressed a second time, the content displayed in the two data digits is recorded in the image register. The alternate register is then displayed with its content and the letter A (Alternate).

- . When the NEX key is depressed a third time, the monitor updates the alternate image register and displays the content of the starting register. The cycle is repeated.

# 3.5.2.2. 16-BIT REGISTERS

- . Depressing the Nex key causes the high byte of the register content to be displayed.

- . When the key is depressed a second time, the high byte is updated and the low byte is displayed with the "\_\_" symbol.

- . When the key is depressed a third time, the low byte is updated and the new value of the high byte is displayed as in the beginning of a new cycle.

- . Practice using your own data to get the feeling of the NEX mode.

#### 3.6. EXECUTION

All programs are merely a set of instructions to be executed sequentially. Sequencing is done by the program counter (PC) which contains at any given time the address of the next program instruction to be executed. Before the EXe key is activated, the PC must be loaded with the address of first program instruction. Once the EXe key is depressed, control remains in the user's program right to the end of the execute operation or until the RES key is depressed.

#### 3.6.1. APPLICATION

The purpose of this exercise is to load 40H into A register, to add OEH to the A content and to store the result into the 1100H memory location. These operations are to be executed by the following program

| ADDRESS              | MACHINE<br>CODE | MNEMONIC   | COMMENTS                                                |  |  |  |

|----------------------|-----------------|------------|---------------------------------------------------------|--|--|--|

| 1000<br>1001         | 3E<br>40        | LDA, 40H   | Load 40H into the A-register                            |  |  |  |

| 1002<br>1003         | C6<br>OE        | ADDA, OEH  | Add OEH to the content of A and record the result in A. |  |  |  |

| 1004<br>1005<br>1006 | 32<br>00<br>11  | LD(1100),A | Transfer the A content to the 1100H memory location.    |  |  |  |

| 1007                 | 76              | HALT       | STOP                                                    |  |  |  |

The MEX and NEX modes are used to load this program as described in paragraph 3.3.

| + MEX     |             | Memory examine mode                                  |

|-----------|-------------|------------------------------------------------------|

| - 1000    | 1 0 0 0     | Address of the first ins-<br>truction                |

| - NEX     | 1 0 0 0 X X | Content of this address=XX                           |

| ~ 3E      | 1 0 0 0 3 3 | Change this content                                  |

| - NEX     | 1 0 0 1 X X | Update and and automatic address increment           |

| - 40      | 1 0 0 1 4 0 | Next byte                                            |

| - NEX, C6 | 1 0 0 2 C 6 |                                                      |

| - NEX, OE | 1 0 0 3 0 E |                                                      |

| - NEX, 32 | 1 0 0 4 3 2 |                                                      |

| - NEX, 00 | 1 0 0 5 0 0 | The low address byte is al-                          |

| - NEX, 11 | 1 0 0 6 1 1 | ways loaded before the high byte in an instruction.  |

| - NEX, 76 | 1 0 0 7 7 6 |                                                      |

| - NEX     | 1 3 0 3 X   | Always depress the NEX key to apdate the last entry. |

This program is now stored in the RAM and is located between memory addresses 1000H a. d 1007H. Let's now check if the 1100H memory location contains the result of the addition.

| - BILLY     |   |   |   |   |   |   |          |

|-------------|---|---|---|---|---|---|----------|

| - 1100, NEX | 1 | 1 | 0 | 0 | Х | Χ | (1100)=X |

The content of the 1100H memory location is not equal to 4EH (40H+0EH=4EH). That's because the program has not yet been executed. Also, it is a good practice to check the program before executing it. After the program has been checked, set the PC to the address of the first instruction (1100H) then depress EXe:

| - REX - PC(5), NEX                  | 5 X X | Register examine                                                                                                                                         |

|-------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| - 10<br>- NEX<br>- 00, NEX<br>- EXe | 5     | Update and display the low byte  Update the low byte and display the high byte.  Execution: the user's program takes the control, the display goes dark. |

We should check the content of 1100H to make sure that the program has been properly executed.

| - RES       | П |   |   |   |   |   |

|-------------|---|---|---|---|---|---|

| - 1100. NEX | 1 | 1 | 0 | 0 | 4 | E |

We find that the content of the 1100H memory location is the sum of 40H and OEH.

#### 3.7. SINGLE STEP

This function is initiated by the SST key. When single stepping, the contents of the image registers are first reloaded into the Z-80 registers. The instruction is then executed and the monitor regains control enabling the contents of the Z-80 registers to be stored away once again in their image registers. The next address in the program, and the content of the accumulator are then displayed. Single stepping provides the user with an efficient method to debug the program under development.

# 3.7.1. APPLICATION

- SST

Using the same program, we will now proceed step by step. The purpose of this exercise is to change 40H to 35H:

| * *        |   |             |   |   |                |   |                                                                                                                                                                                  |

|------------|---|-------------|---|---|----------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - REX      | r |             |   |   |                |   | Examine register mode                                                                                                                                                            |

| - PC, NEX  | 5 |             |   |   | Х              | Х |                                                                                                                                                                                  |

| - 10 , NEX | 5 |             |   |   | Х              | Х | Initialization of the pro-                                                                                                                                                       |

| - 00. NEX  | 5 |             |   |   | 1              | 0 | gram counter.                                                                                                                                                                    |

| - SST      | 1 | 0           | 0 | 2 | L <sub>L</sub> | 0 | The first instruction is                                                                                                                                                         |

|            |   | · · · · · · |   |   |                |   | executed; the monitor displays the address of the next instruction and the content of the accumulator                                                                            |

| - REX, A   | A |             |   |   |                |   | (A-register)                                                                                                                                                                     |

| - NEX, 35  | Α |             |   |   | 3              | 5 | Change 40Hto 35H                                                                                                                                                                 |

| - NEX      | А |             |   | А | X              | Х | Acquisition; (A)=35                                                                                                                                                              |

| - SST      | 1 | 0           | 0 | 4 | 4              | 3 | The second instruction is executed; the content of the accumulator is displayed (result of the addition: 35H + OEH = 43H); the Points to the address of the next executable ins- |

|            | 1 | 0           | 0 | 7 | L <sub>4</sub> | 3 | truction.                                                                                                                                                                        |

The content of the accumulator is transfered to

the 1100H memory location; the program counter points to the address of

the last executable ins-

truction (HALT).

| - MEX       | г |   |   |   |   |   |

|-------------|---|---|---|---|---|---|

| - 1100, NEX | 1 | 1 | 0 | 0 | 4 | 3 |

| - SST       | 1 | 0 | 0 | 8 | 4 | 3 |

Return to the MEX mode to check the content of 1100H memory location.

(1100H) = 43H

The accumulator has not executed any operation and its content remains the same; the PC content is incremented by 1 to point to the next memory address (outside of program).

# 3.8. CASSETTE RECORDING

The PRO-80 offers a simple and inexpensive way to record on a cassette tape the volatile information stored in the RAM. Most audio cassette recorders can be used, however if you are planning to buy one for this purpose, we suggest you consider the 26-1206 model CTR-80 from Radio Shack. The transfer sequence is the following:

- Connect the "AUX" jack on the PRO-80 to the auxiliary input of the cassette recorder.

- Fully rewind the cassette

- Using the MEX mode enter the address of the last byte in the program to be recorded into the following memory locations:

- . 13DCH: Low address byte

- · 13DDH: High address byte

- Remember to depress the NEX key to validate the last entry.

- Turn the volume control to a half way setting.

- Initiate the cassette writefunction by depressing the CW key.

- Set the recorder in the record mode; the display unit will go dark.

- The " " prompt sign reappears when the recording is complete.

# 3.9 CASSETTE READ

To transfer a program from a cassette to a RAM, simply follow these steps:

- Plug the CASS connector on your PRO-80 into the earphone (or monitor) jack on your recorder.

- Rewind the cassette and set the recorder in the play mode.

- Adjust the volume control so that the LED becomes very bright. (the volume control will most likely have to be set to maximum.)

- Depress the RES key on your PRO-80.

- Initiate the read function by depressing the CR push button; the display unit will go dark during the transfer.

- If the transfer is successful, the monitor returns to the MEX mode and displays the " " prompt sign.

- If an error is detected during the transfer, the monitor displays the letter "r" in the first leftmost digit position. Check the volume and repeat the same procedure or check the program being read using the MEX mode and correct any error.

#### NOTE:

- 1. The more experienced reader will soon realize that it is not easy to carry out all PRO-80 functions with only a 1 Kbyte monitor. Because of such space limitations, the PRO-80 monitor can not record a program at just any RAM address. To be recorded all programs must be located at starting address 1000H.

- 2. The user can easily record and locate several programs on a single cassette thanks to the LED which is lit when data is present and off between recordings.

## IV APPLICATION PROGRAMS

The reader must be familiar with the Z-80 set of instructions to understand the programs discussed in this chapter. Those who have had prior experience with machine language programming can refer directly to the "Micro-Reference Manual" which summarizes the Z-80 set of instructions. If you have no such experience consult: "Programming the Z-80" by Rodnay Zaks, Sybex, or any book dealing with the Z-80 instructions.

## 4.1. CHASER LIGHTS

The purpose of this simulation is to help the reader understand how the PRO-80 display unit works and how to write a program for a chaser light display.

Annex 1 represents the electronic diagram of the PRO-80 display unit. The functional illustration of the unit is in figure 4.1.

Figure 4.1: Functional diagram of the PRO-80 display unit.

This figure shows that each digit is made up of seven segments; a, b, c, d, e, f, and g. Each segment lights up when its corresponding bit at port 4CH is set to "1". The content of port 48H selects the active digit. For instance the first rightmost digit is active when the least significant bit is at logical "0", the second digit is active when the first order bit is at logical "0" and so on. If we wanted the first rightmost digit to be a 9, the content of the two ports would have to be:

| Port 4CH | Х | 1 | 1 | 0 | 1 | 1 | 1 | 1 | =(6FH) |

|----------|---|---|---|---|---|---|---|---|--------|

| Port 48H | Х | Х | 1 | 1 | 1 | 1 | 1 | 0 | =(3EH) |

Exercise: We want the second rightmost digit to be a 3. Give the content of each port.

Answer: (Port 4CH) = 4FH(Port 48H) = 3DH

To simulate chaser lights, we will be using segments c, d, e and g of each digit. If we want the "square" to move from right to left, the program sequence is the following:

- 1. Load the segment select word into the accumulator.

- 2. Transfer the content of the accumulator to port 4CH to activate the segments.

- 3. Load the digit select word into the accumulator.

- 4. Transfer the content of the accumulator.

- 5. Create a display delay.

- 6. Shift the content of the accumulator one position to the left to activate the next digit.

- 7. Loop to step 4 so the shift is repeated indefinitely.

- X: This digit is not used by the display unit and can therefore be either "0" or "1". The "0" value has arbitrarily been given.

#### NOTE:

The display delay allows the operator to see the digits moving. Without it, the microcomputer operates at such speed that the all digits will appear to be always lit.

To create a delay we can for instance tell the processor to decrement a register already loaded with a value which determines the waiting time. When the content of the register becomes null, the processor continues to execute the remaining program instructions. If this delay is not long enough (as is presently the case), two or more registers may be used.

#### PROGRAM SEQUENCE:

| 1000         | 3EDC                 |         | LDA, DCH     | Content of A=DCH                      |

|--------------|----------------------|---------|--------------|---------------------------------------|

| 1002         | D34C                 |         | OUT (4CH),A  | Activate segments C,D,E,G.            |

| 1004         | 3EFE                 |         | LDA, FEH     | (A)=FE                                |

| 1006         | D348                 | Loop 3: | OUT (48H),A  | Select the 1 <sup>st</sup> digit      |

| 1008         | 0E40                 |         | LDC, 40H     | Initialize the first delay register.  |

| 100A         | 06FF                 | Loop 2: | LDB, FFH     | Initialize the second delay register. |

| 100C         | 10FE                 | Loop 1: | DJNZ, Loop1. | Decrement B to OH                     |

| 100E         | OD                   |         | DEC C        | Decrement C by 1.                     |

| <b>1</b> 00F | 20F9                 |         | JRNZ,Loop 2: | Jump to loop 2 except if C=OH         |

| 1011         | 07                   |         | RLCA         | Next digit.                           |

| 1012         | <b>1</b> 8F <b>2</b> |         | JR Loop 3:   | Jump to loop 3.                       |

After studying this program, load it using the MEX mode. Find a simple way to:

- 1. Slow down the speed at which the square moves.

- 2. Replace the "  $\Box$  " sign by another sign of your choice.

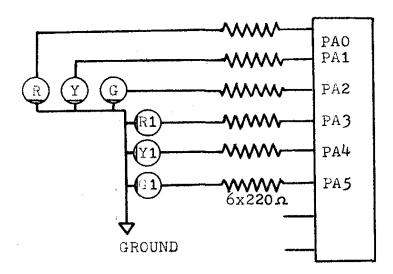

#### 4.2. TRAFFIC LIGHTS

It would again be possible to use the display unit to simulate traffic lights but why not take this opportunity to try out your PRO-80 PIO. For this exercise, get two red, two yel-

low and two green LEDs  $^{(1)}$  and six 220  $\Omega$  ,  $\frac{1}{4}$  W resistances to be assembled as follows:

Here is the instruction sequence:

- a- Initialization: R and G1 are lit

- b- Long delay

- c- R and Y1 are lit

- d- Short delay

- e- R1 and G are lit

- f- Long delay

- g- R1 and Y are lit

- h- Short delay

- i- Loop to (a)

#### a- Initialization

Before the initialization begins, the PIO A-register must be set as an output port. Its control register (port 42H) should have the following content: (Consult your Micro-Reference Manual, page 25)

| Port | (42H)  | 0 | 0 | Х | Х | 1 | 1 | 1 | 1 | (A | control  | register) |   |

|------|--------|---|---|---|---|---|---|---|---|----|----------|-----------|---|

| POLC | (4211) |   |   |   |   |   |   |   |   | (  | 00110101 | 105200017 | ٠ |

(1) LED: Light-emitting diode.

The A-register is configured as an output port when DO to D3 are at "1" and D6-D7 are at "0". Select either O or 1 for D4 and D5. The control word is 0000 1111 (0FH).

The A-register can now be initialized. R and G1 must be lit; D0 and D5 are therefore at "1". All other lines are at "0" except for D6 and D7 which are ignored. The A-register (port 40H) will contain the following value:

Port A (40H) 0 0 1 0 0 0 0 1 (21H)

b- LONG DELAY

Since a delay will often be used, we suggest you to write a delay routine that could be called once for a short delay and n times for a long delay.

## c- R AND YI ARE LIT

Data lines DO and D4 must be set to "1", and all others must be at "0". The new control word transfered to port A is:

Port (40H) 0 0 1 0 0 0 1 (11H)

The word OCH is sent to port A to light R1 and G and the word OAH is sent to light R1 and Y.

#### PROGRAM

| 1000         | 3E OF        |      | LDA, OFH     | Configuration of the A re- |

|--------------|--------------|------|--------------|----------------------------|

| 1002         | D3 42        |      | OUT(42H), A  | gister as an output port.  |

| 1004         | 3E 21        | BR3: | LDA, 21H     |                            |

| 1006         | D3 40        |      | OUT (40H), A | R and G1 light up          |

| 1008         | 06 OA        |      | LDB, OAH     |                            |

| 100A         | CD 2A10      | BR1: | CALL DELAY   | Long Delay                 |

| 100D         | <b>10</b> FB |      | DJNZ, BR1    |                            |

| <b>100</b> F | 3E 11        |      | LDA, 11H     |                            |

| 1011         | D3 40        |      | OUT (40H),A  | R and Y1 light up          |

| 1013         | CD 2A10      |      | CALL DELAY   | Short delay                |

| <b>101</b> 6 | 3E OC        |      | LDA, OCH     |                            |

| <b>101</b> 8 | D3 40       |               | OUT (40H),A        | R1 and G light up             |

|--------------|-------------|---------------|--------------------|-------------------------------|

| 101A         | 06 OA       |               | LDB, OAH           |                               |

| 101C         | CD 2A10     | BR2 :         | CALL DELAY         | LONG DELAY                    |

| 101F         | 10 FB       |               | DJNZ, BR2          |                               |

| 1021         | 3E OA       |               | LDA, OAH           |                               |

| 1023         | D3 40       |               | OUT(40H),A         |                               |

| 1025         | CD 2A10     |               | CALL DELAY         | Short delay                   |

| 1028         | 18 D9       |               | JR,BR3             | Loop                          |

|              |             | DI            | ELAY ROUTINE       |                               |

| 102A         | C <b>5</b>  |               | PUSH B             | Save B and C                  |

| 102B         | OE OB       |               | LDC, OB            | Initialize the first counter  |

| 102D         | 06 FF       | BR <b>5</b> : | LDB, FF            | Initialize the second counter |

| <b>10</b> 2F | 10 FE       | BR4 :         | DJNZ, BR4          | Decrement B to "0"            |

| 1031         |             |               |                    |                               |

| -            | OD          |               | DEC C              | Decrement C                   |

| 1032         | OD<br>20 F9 |               | DEC C<br>JRNZ, BR5 |                               |

| -            |             |               |                    |                               |

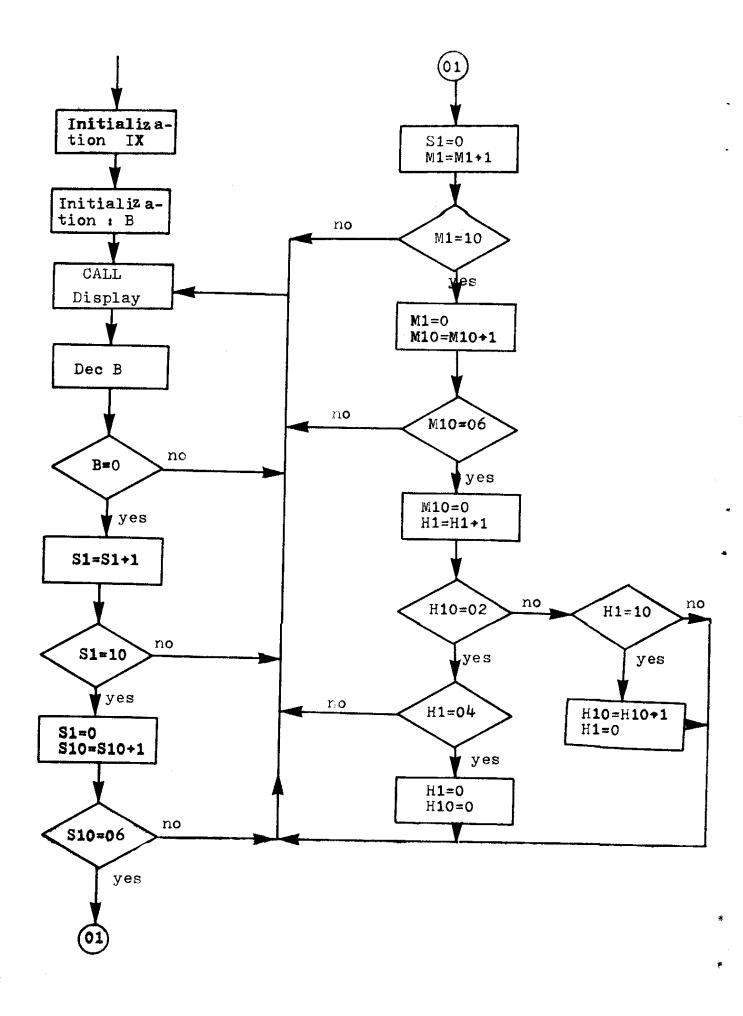

## 4.3. DIGITAL CLOCK

We have seen in paragraph 4.1. how to activate a single digit of the display unit. Now, for several digits to appear lit at the same time, we must use the multiplexing technique. This technique consists in displaying sequentially one digit at a time and repeating the sequence fast enough so that the human eye cannot tell when the digits are not lit. Remember that in North America, alternating voltage shut off 120 times per second. For instance, the common neon tube is in fact shut off 120 times per second. It appears to be always lit because it is on for a longer time than it is off and at this frequency the retina is unable to tell when it is off

and only senses the mean intensity of the light being emitted.

The digital clock simulation program is written in two steps; in the first, a display routine is created which fetches the content of a buffer and converts it in order to generate and display the required number.

The second step consists in writing a program which will use the display routine to simulate a digital clock.

#### DISPLAY ROUTINE :

We must first of all define a look up table which will generate the control character required to light up each decimal digit (0 to 9). If for instance the starting address is 1200H, we would have the following table:

| ADDRESS       | CONTROL<br>CHARACTER | DIGIT |

|---------------|----------------------|-------|

| <b>1200</b> H | <b>3</b> FH          | 0     |

| 1201H         | 06н                  | 1     |

| 1202H         | <b>5</b> BH          | 2     |

| 1203H         | 4FH                  | 3     |

| 1204H         | 66н                  | 4     |

| 1205H         | 6рн                  | 5     |

| 1206Н         | 7DH                  | 6     |

| 1207H         | 07Н                  | 7     |

| <b>120</b> 8H | 7FH                  | 8     |

| 1209H         | 6FH                  | 9     |

The next step would be to define six memory locations containing at any given moment a time value, especially the setting time.

| (1210H) | =  | seconds (units) | S1          |

|---------|----|-----------------|-------------|

| (1211H) | == | seconds (tens)  | S <b>10</b> |

| (1212H) | == | minutes (units) | M1          |

| (1213H) | =  | minutes (tens)  | M10         |

| (1214H) | =  | hours (units)   | H <b>1</b>  |

| (1215H) | =  | hours (tens)    | H <b>10</b> |

Now, we must follow the sequence below:

- Load the content of 1210H (S1) into a register.

- Find the control character in the look up table.

- Display it in the first rightmost digit position.

- Create a delay so that the digit remains displayed for a while.

- Clear this digit.

- Increment the starting address to select S10.

- Repeat the procedure until the six digits have been displayed.

## CLOCK SIMULATION PROGRAM

The algorithm found on page 52 is a summary of the following program:

|              |                |                 | •                       |

|--------------|----------------|-----------------|-------------------------|

| 1000         | DD211012       | LDIX, 1210H     | Pointer initialization  |

| 1004         | 0610           | LDB, 10H        | 1 second initialization |

| 1006         | CD7310 BR1 :   | CALL DISPLAY    | Call display            |

| 1009         | <b>10</b> FB   | DJNZ, BR1       | 1s delay loop           |

| <b>100</b> B | DD3400         | INC (IX +0)     | SEC1 increment          |

| <b>100</b> E | 3E0A           | LDA, OAH        |                         |

| 1010         | DDBE00         | CP (IX + 0),    | TEST SEC 1=10           |

| 1013         | 20F1           | JRNZ,BR1        | Loop to display         |

| 1015         | DD360000       | LD(IX + 0),00H  | SEC1=0                  |

| 1019         | DD3401         | INC (IX+1)      | SEC10 increment         |

| 101C         | 3E06           | LDA,06H         |                         |

| 101E         | DDBE <b>01</b> | CP (IX + 1)     | Test sec 10=06          |

| 1021         | 20正3           | JRNZ,BR1        | Loop to display         |

| 1023         | DD 360100      | LD (IX + 1),00H | SEC 10=0                |

| 1027         | DD3402         | INC (IX + 2)    | M1 increment            |

| 102A         | 3EOA           | LDA,OAH         |                         |

| 102C         | DDBE02         | CP (IX + 2)     | TEST M1=10              |

| 102F         | 20D5           | JRNZ,BR1        | Loop to display         |

| 1031         | DD360200       | LD (IX + 2),00H | M1=0                    |

| 1035         | DD3403         | INC (IX +3)     | M10 increment           |

| 1038         | 3E <b>0</b> 6  | LDA, 06H        |                         |

| 103A         | DDBE03         | CP (IX + 3)     | Test M10 = 06           |

| 103D         | 20 D7          | JRNZ,BR1        | Loop to display         |

| 10 3F        | DD360300       | LD (IX + 3),00H | M10=0                   |

| 1043         | DD3404          |      | INC $(IX + 4)$  | H1 increment            |

|--------------|-----------------|------|-----------------|-------------------------|

| 1046         | 3E02            |      | LDA,02H         |                         |

| <b>10</b> 48 | DDBE05          |      | CP (IX + 5)     | TEST H1=02              |

| <b>10</b> 4B | 2003            |      | JRNZ, BR2       |                         |

| 104D         | C36110          |      | JP, BR3         | H1 = 02                 |

| 1050         | 3E <b>0</b> A   | BR2: | LDA, OA         |                         |

| 1052         | DDBE04          |      | CP (IX + 4)     | TEST H1 = 10            |

| 1055         | 20AF            |      | JRNZ,BR1        | Loop to display         |

| 10 57        | DD360400        |      | LD (IX + 4),00H | H1 = 0                  |

| <b>10</b> 5B | DD3405          |      | INC (IX + 5)    | H10 increment           |

| <b>10</b> 5E | C30610          |      | JP,BR1          | Loop to display         |

| 1061         | 3E04            | BR3: | LDA,04H         |                         |

| 1063         | DDBE <b>0</b> 4 |      | CP (IX + 4)     | TEST H10 = 04           |

| 1066         | 209E            |      | JRNZ,BR1        | LOOP to display         |

| 1068         | DD360400        |      | LD (IX + 4),00H | H1 = 0                  |

| <b>10</b> 60 | DD360500        |      | LD (IX + 5),00H | H10 = 0                 |

| 1070         | C <b>30610</b>  |      | JP, BR1         |                         |

|              |                 |      | DISPLAY ROUTINE |                         |

| 1073         | OEFE            |      | LDC, FEH        |                         |

| 1075         | 211012          |      | LDHL, 1210H     | Pointer initialization  |

| 1078         | 5E              | BR5: | LDE, (HL)       |                         |

| 1079         | 1612            |      | LDD, 12         | (DE) = CONTROL CARACTER |

| <b>10</b> 7B | 79              |      | LDA,(C)         |                         |

| <b>10</b> 70 | D348            |      | OUT (48H), A    | Active digit            |

| 107E         | 1A              |      | LDA, (DE)       |                         |

| <b>10</b> 7F | D34C            |      | OUT (4CH) ,A    | Active segments         |

| 1081         | 3E4B       |      | LDA, 4BH      | Display delay           |

|--------------|------------|------|---------------|-------------------------|

| 1083         | <b>3</b> D | BR4: | DECA          |                         |

| 1084         | 20 FD      |      | JRNZ,BR4      |                         |

| 1086         | D34C       |      | OUT (4CH),A   | Reset all segments      |

| <b>108</b> 8 | 23         |      | INC HL        | Next digit              |

| 1089         | CB01       | •    | RLC, C        |                         |

| <b>10</b> 8B | CB71       |      | BIT6, C       | Test end of display     |